# SECTION 17 TIME PROCESSOR UNIT 3

The time processor unit 3 (TPU3), an enhanced version of the original TPU, is an intelligent, semi-autonomous microcontroller designed for timing control. The TPU3 is fully compatible to the TPU2. Operating simultaneously with the CPU, the two TPU3 modules process micro-instructions, schedules and processes real-time hardware events, performs input and output, and accesses shared data without CPU intervention. Consequently, for each timer event, the CPU setup and service times are minimized or eliminated.

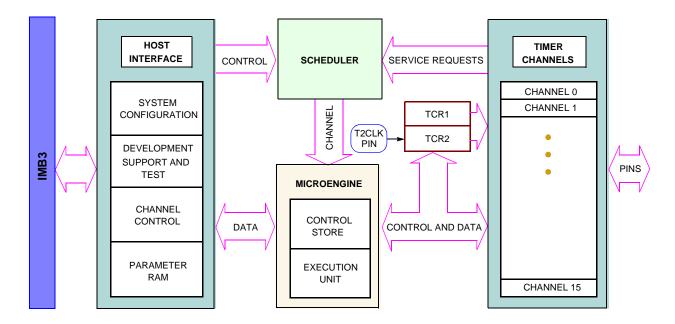

The MPC555 contains two independent TPU3s. **Figure 17-1** is a simplified block diagram of a single TPU3.

Figure 17-1 TPU3 Block Diagram

#### 17.1 Overview

The TPU3 can be viewed as a special-purpose microcomputer that performs a programmable series of two operations, match and capture. Each occurrence of either operation is called an event. A programmed series of events is called a function. TPU functions replace software functions that would require CPU interrupt service.

The microcode ROM TPU3 functions that are available in the MPC555 are described in **APPENDIX D TPU ROM FUNCTIONS**.

#### 17.2 TPU3 Components

The TPU3 consists of two 16-bit time bases, 16 independent timer channels, a task scheduler, a microengine, and a host interface. In addition, a dual-ported parameter RAM is used to pass parameters between the module and the CPU.

#### 17.2.1 Time Bases

Two 16-bit counters provide reference time bases for all output compare and input capture events. Prescalers for both time bases are controlled by the CPU via bit fields in the TPU3 module configuration register (TPUMCR) and TPU module configuration register two (TPUMCR2). Timer count registers TCR1 and TCR2 provide access to the current counter values. TCR1 and TCR2 can be read by TPU microcode but are not directly available to the CPU. The TCR1 clock is always derived from the system clock. The TCR2 clock can be derived from the system clock or from an external input via the T2CLK clock pin. The duration between active edges on the T2CLK clock pin must be at least nine system clocks.

#### 17.2.2 Timer Channels

The TPU3 has 16 independent channels, each connected to an MCU pin. The channels have identical hardware and are functionally equivalent in operation. Each channel consists of an event register and pin control logic. The event register contains a 16-bit capture register, a 16-bit compare/match register, and a 16-bit greater-than-or-equal-to comparator. The direction of each pin, either output or input, is determined by the TPU microengine. Each channel can either use the same time base for match and capture, or can use one time base for match and the other for capture.

#### 17.2.3 Scheduler

When a service request is received, the scheduler determines which TPU3 channel is serviced by the microengine. A channel can request service for one of four reasons: for host service, for a link to another channel, for a match event, or for a capture event. The host system assigns each active channel one of three priorities: high, middle, or low. When multiple service requests are received simultaneously, a priority-scheduling mechanism grants service based on channel number and assigned priority.

#### 17.2.4 Microengine

The microengine is composed of a control store and an execution unit. Control-store ROM holds the microcode for each factory-masked time function. When assigned to a channel by the scheduler, the execution unit executes microcode for a function assigned to that channel by the CPU. Microcode can also be executed from the dual-port RAM (DPTRAM) module instead of the control store. The DPTRAM allows emulation and development of custom TPU microcode without the generation of a microcode ROM mask. Refer to 17.3.6 Emulation Support for more information.

#### 17.2.5 Host Interface

The host interface registers allow communication between the CPU and the TPU3, both before and during execution of a time function. The registers are accessible from the IMB through the TPU3 bus interface unit. Refer to **17.4 Programming Model** for register bit/field definitions and address mapping.

#### 17.2.6 Parameter RAM

Parameter RAM occupies 256 bytes at the top of the system address map. Channel parameters are organized as 128 16-bit words. Channels zero through 15 each have eight parameters. The parameter RAM address map in 17.4.18 TPU3 Parameter RAM shows how parameter words are organized in memory.

The CPU specifies function parameters by writing to the appropriate RAM address. The TPU3 reads the RAM to determine channel operation. The TPU3 can also store information to be read by the CPU in the parameter RAM. Detailed descriptions of the parameters required by each time function are beyond the scope of this manual. Refer to the *TPU Reference Manual* (TPURM/AD) and the Motorola TPU Literature Package (TPULITPAK/D) for more information.

#### 17.3 TPU Operation

All TPU3 functions are related to one of the two 16-bit time bases. Functions are synthesized by combining sequences of match events and capture events. Because the primitives are implemented in hardware, the TPU3 can determine precisely when a match or capture event occurs, and respond rapidly. An event register for each channel provides for simultaneous match/capture event occurrences on all channels.

When a match or input capture event requiring service occurs, the affected channel generates a service request to the scheduler. The scheduler determines the priority of the request and assigns the channel to the microengine at the first available time. The microengine performs the function defined by the content of the control store or emulation RAM, using parameters from the parameter RAM.

#### 17.3.1 Event Timing

Match and capture events are handled by independent channel hardware. This provides an event accuracy of one time-base clock period, regardless of the number of channels that are active. An event normally causes a channel to request service. The time needed to respond to and service an event is determined by which channels and the number of channels requesting service, the relative priorities of the channels requesting service, and the microcode execution time of the active functions. Worst-case event service time (latency) determines TPU3 performance in a given application. Latency can be closely estimated. For more information, refer to the *TPU Reference Manual* (TPURM/AD).

#### 17.3.2 Channel Orthogonality

Most timer systems are limited by the fixed number of functions assigned to each pin. All TPU3 channels contain identical hardware and are functionally equivalent in oper-

ation, so that any channel can be configured to perform any time function. Any function can operate on the calling channel, and, under program control, on another channel determined by the program or by a parameter. The user controls the combination of time functions.

#### 17.3.3 Interchannel Communication

The autonomy of the TPU3 is enhanced by the ability of a channel to affect the operation of one or more other channels without CPU intervention. Interchannel communication can be accomplished by issuing a link service request to another channel, by controlling another channel directly, or by accessing the parameter RAM of another channel.

#### 17.3.4 Programmable Channel Service Priority

The TPU3 provides a programmable service priority level to each channel. Three priority levels are available. When more than one channel of a given priority requests service at the same time, arbitration is accomplished according to channel number. To prevent a single high-priority channel from permanently blocking other functions, other service requests of the same priority are performed in channel order after the lowest-numbered, highest-priority channel is serviced.

#### 17.3.5 Coherency

For data to be coherent, all available portions of the data must be identical in age, or must be logically related. As an example, consider a 32-bit counter value that is read and written as two 16-bit words. The 32-bit value is read-coherent only if both 16-bit portions are updated at the same time, and write-coherent only if both portions take effect at the same time. Parameter RAM hardware supports coherent access of two adjacent 16-bit parameters. The host CPU must use a long-word operation to guarantee coherency.

# **17.3.6 Emulation Support**

Although factory-programmed time functions can perform a wide variety of control tasks, they may not be ideal for all applications. The TPU3 provides emulation capability that allows the user to develop new time functions. Emulation mode is entered by setting the EMU bit in TPUMCR. In emulation mode, an auxiliary bus connection is made between the DPTRAM and the TPU3, and access to DPTRAM via the intermodule bus is disabled. A 9-bit address bus, a 32-bit data bus, and control lines transfer information between the modules. To ensure exact emulation, DPTFLASH module access timing remains consistent with access timing of the TPU microcode ROM control store.

To support changing TPU application requirements, Motorola has established a TPU function library. The function library is a collection of TPU functions written for easy assembly in combination with each other or with custom functions. Refer to Motorola Programming Note TPUPN00/D, *Using the TPU Function Library and TPU Emulation Mode* for information about developing custom functions and accessing the TPU function.

tion library. Refer to the Motorola TPU Literature Package (TPULITPAK/D) for more information about specific functions.

#### 17.3.7 TPU3 Interrupts

Each of the TPU3 channels can generate an interrupt service request. Interrupts for each channel must be enabled by writing to the appropriate control bit in the channel interrupt enable register (CIER). The channel interrupt status register (CISR) contains one interrupt status flag per channel. Time functions set the flags. Setting a flag bit causes the TPU3 to make an interrupt service request if the corresponding channel interrupt enable bit is set.

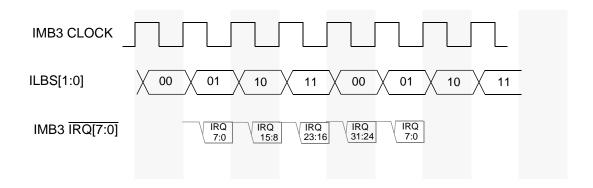

The TPU3 can generate one of 32 possible interrupt request levels on the IMB3. The value driven onto  $\overline{\text{IRQ[7:0]}}$  represents the interrupt level programmed in the IRL field of the TPU interrupt configuration register (TICR). Under the control of the ILBS bits in the ICR, each interrupt request level is driven during the time multiplexed bus during one of four different time slots, with eight levels communicated per time slot. No hardware priority is assigned to interrupts. Furthermore, if more than one source on a module requests an interrupt at the same level, the system software must assign a priority to each source requesting at that level. **Figure 17-2** displays the interrupt level scheme.

Figure 17-2 TPU3 Interrupt Levels

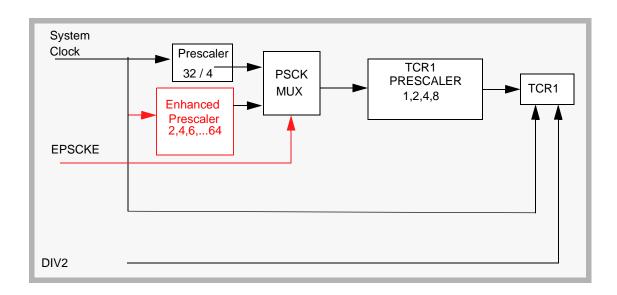

#### 17.3.8 Prescaler Control for TCR1

Timer count register 1 (TCR1) is clocked from the output of a prescaler. The following fields control TCR1:

- The PSCK and TCR1P fields in TPUMCR

- The DIV2 field in TPUMCR2

- The EPSCKE and EPSCK fields in TPUMCR3.

The rate at which TCR1 is incremented is determined as follows:

• The user selects either the standard prescaler (by clearing the enhanced prescaler enable bit, EPSCKE, in TPUMCR3) or the enhanced prescaler (by setting EPSCKE).

If the standard prescaler is selected (EPSCKE = 0), the the PSCK bit determines whether the standard prescaler divides the system clock input by 32 (PSCK = 0) or four (PSCK = 1)

— If the enhanced prescaler is selected (EPSCKE = 1), the EPSCK bits select a value by which the system clock is divided. The lowest frequency for TCR1 clock is system clock divided by 64x8. The highest frequency for TCR1 clock is system clock divided by two (2x1). See Table 17-1.

Table 17-1 Enhanced TCR1 Prescaler Divide Values

| EPSCK Value     | Divide System Clock By |

|-----------------|------------------------|

| 0x00            | 2                      |

| 0x01            | 4                      |

| 0x02            | 6                      |

| 0x03            | 8                      |

| 0x04, 0x05,0x1d | 10,12,60               |

| 0x1e            | 62                     |

| 0x1f            | 64                     |

— The output of either the standard prescaler or the enhanced prescaler is then divided by 1, 2, 4, or 8, depending on the value of the TCR1P field in the TPUMCR.

**Table 17-2 TCR1 Prescaler Values**

| TCR1P Value | Divide by |

|-------------|-----------|

| 0b00        | 1         |

| 0b01        | 2         |

| 0b10        | 4         |

| 0b11        | 8         |

— If the DIV2 bit is one, the TCR1 counter increments at a rate of the internal clock divided by two. If DIV2 is zero, the TCR1 increment rate is defined by the output of the TCR1 prescaler (which, in turn, takes as input the output of either the standard or enhanced prescaler).

Figure 17-3 shows a diagram of the TCR1 prescaler control block.

Figure 17-3 TCR1 Prescaler Control

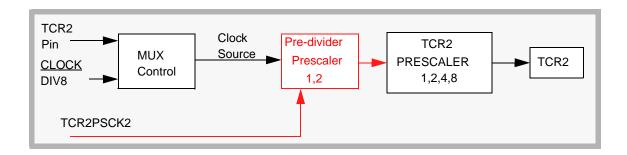

#### 17.3.9 Prescaler Control for TCR2

Timer count register 2 (TCR2), like TCR1, is clocked from the output of a prescaler. The T2CG (TCR2 clock/gate control) bit and the T2CSL (TCR2 counter clock edge) bit in TPUMCR determine T2CR2 pin functions. Refer to **Table 17-3**.

| T2CSL | T2CG | TCR2 Clock                   |

|-------|------|------------------------------|

| 0     | 0    | Rise transition T2CLK        |

| 0     | 1    | Gated system clock           |

| 1     | 0    | Fall transition T2CLK        |

| 1     | 1    | Rise & fall transition T2CLK |

**Table 17-3 TCR2 Counter Clock Source**

The function of the T2CG bit is shown in Figure 17-4.

When T2CG is set, the external T2CLK pin functions as a gate of the DIV8 clock (the TPU3 system clock divided by eight). In this case, when the external TCR2 pin is low, the DIV8 clock is blocked, preventing it from incrementing TCR2. When the external TCR2 pin is high, TCR2 is incremented at the frequency of the DIV8 clock. When T2CG is cleared, an external clock from the TCR2 pin, which has been synchronized and fed through a digital filter, increments TCR2. The duration between active edges on the T2CLK clock pin must be at least nine system clocks.

The TCR2PSCK2 bit in TPUMCR3 determines whether the clock source is divided by two before it is fed into the TCR2 prescaler. The TCR2 field in TPUMCR specifies the value of the prescaler: 1, 2, 4, or 8. Channels using TCR2 have the capability to

resolve down to the TPU3 system clock divided by eight. Figure 17-4 illustrates the TCR2 pre-divider and pre-scaler control.

Figure 17-4 TCR2 Prescaler Control

**Table 17-4** is a summary of prescaler output (assuming a divide-by-one value for the pre-divider prescaler.

**Internal Clock Divide Ratio External Clock Divide Ratio TCR2 Value** TCR2PSCK2 = 0 TCR2PSCK2 = 1 TCR2PSCK2 = 0 TCR2PSCK2 = 1 0b00 8 8 1 0b01 16 24 2 3 32 7 0b10 56 4 0b11 120 8 15

**Table 17-4 TCR2 Prescaler Control**

#### 17.4 Programming Model

The TPU3 memory map contains three groups of registers:

- System configuration registers

- Channel control and status registers

- Development support and test verification registers

All registers except the channel interrupt status register (CISR) must be read or written by means of half-word (16-bit) or word (32-bit) accesses. The address space of the TPU3 memory map occupies 512 bytes. Unused registers within the 512-byte address space return zeros when read.

**Table 17-5** shows the TPU3 address map.

# Table 17-5 TPU3 Register Map

|                        | MSB<br>0                                                                                   | LSB<br>15 |

|------------------------|--------------------------------------------------------------------------------------------|-----------|

| Address                | Register                                                                                   | 10        |

| 0x30 4000              | TPU3 Module Configuration Register (TPUMCR)                                                |           |

| 0x30 4400              | See Table 17-6 for bit descriptions.                                                       |           |

| 0x30 4002              | TPU3 Test Configuration Register (TCR)                                                     |           |

| 0x30 4402              |                                                                                            |           |

| 0x30 4004<br>0x30 4404 | Development Support Control Register (DSCR) See Table 17-7 for bit descriptions.           |           |

| 0x30 4006              | Development Support Status Register (DSSR)                                                 |           |

| 0x30 4406              | See Table 17-8 for bit descriptions.                                                       |           |

| 0x30 4008              | TPU3 Interrupt Configuration Register (TICR)                                               |           |

| 0x30 4408              | See Table 17-9 for bit descriptions.                                                       |           |

| 0x30 400A<br>0x30 440A | Channel Interrupt Enable Register (CIER) See Table 17-10 for bit descriptions.             |           |

| 0x30 400C              | Channel Function Selection Register 0 (CFSR0)                                              |           |

| 0x30 440C              | See Table 17-11 for bit descriptions.                                                      |           |

| 0x30 400E              | Channel Function Selection Register 1 (CFSR1)                                              |           |

| 0x30 440E              | See Table 17-11 for bit descriptions.                                                      |           |

| 0x30 4010<br>0x30 4410 | Channel Function Selection Register 2 (CFSR2) See Table 17-11 for bit descriptions.        |           |

| 0x30 4012              | Channel Function Selection Register 3 (CFSR3)                                              |           |

| 0x30 4412              | See <b>Table 17-11</b> for bit descriptions.                                               |           |

| 0x30 4014              | Host Sequence Register 0 (HSQR0)                                                           |           |

| 0x30 4414              | See Table 17-12 for bit descriptions.                                                      |           |

| 0x30 4016<br>0x30 4416 | Host Sequence Register 1 (HSQR1) See Table 17-12 for bit descriptions.                     |           |

| 0x30 4018              | Host Service Request Register 0 (HSRR0)                                                    |           |

| 0x30 4418              | See Table 17-13 for bit descriptions.                                                      |           |

| 0x30 401A              | Host Service Request Register 1 (HSRR1)                                                    |           |

| 0x30 441A              | See Table 17-13 for bit descriptions.                                                      |           |

| 0x30 401C<br>0x30 441C | Channel Priority Register 0 (CPR0) See Table 17-14 for bit descriptions.                   |           |

| 0x30 401E              | Channel Priority Register 1 (CPR1)                                                         |           |

| 0x30 441E              | See <b>Table 17-14</b> for bit descriptions.                                               |           |

| 0x30 4020              | Channel Interrupt Status Register (CISR)                                                   |           |

| 0x30 4420              | See Table 17-16 for bit descriptions.                                                      |           |

| 0x30 4022<br>0x30 4422 | Link Register (LR)                                                                         |           |

| 0x30 4024              |                                                                                            |           |

| 0x30 4424              | Service Grant Latch Register (SGLR)                                                        |           |

| 0x30 4026              | Decoded Channel Number Register (DCNR)                                                     |           |

| 0x30 4426              |                                                                                            |           |

| 0x30 4028<br>0x30 4428 | TPU Module Configuration Register 2 (TPUMCR2) See <b>Table 17-17</b> for bit descriptions. |           |

| 0x30 4428              | TPU Module Configuration 3 (TPUMCR3)                                                       |           |

| 0x30 442A              | See <b>Table 17-20</b> for bit descriptions.                                               |           |

| 0x30 402C              |                                                                                            |           |

| 0x30 442C              | Internal Scan Data Register (ISDR)                                                         |           |

# Table 17-5 TPU3 Register Map (Continued)

|                                                | MOD                                   |

|------------------------------------------------|---------------------------------------|

|                                                | MSB<br>0                              |

| Address                                        | Register                              |

| 0x30 402E<br>0x30 442E                         | Internal Scan Control Register (ISCR) |

| 0x30 4100 – 0x30 410F<br>0x30 4500 – 0x30 450F | Channel 0 Parameter Registers         |

| 0x30 4110 - 0x30 411F<br>0x30 4510 - 0x30 451F | Channel 1 Parameter Registers         |

| 0x30 4120 - 0x30 412F<br>0x30 4520 - 0x30 452F | Channel 2 Parameter Registers         |

| 0x30 4130 - 0x30 413F<br>0x30 4530 - 0x30 453F | Channel 3 Parameter Registers         |

| 0x30 4140 - 0x30 414F<br>0x30 4540 - 0x30 454F | Channel 4 Parameter Registers         |

| 0x30 4150 - 0x30 415F<br>0x30 4550 - 0x30 455F | Channel 5 Parameter Registers         |

| 0x30 4160 - 0x30 416F<br>0x30 4560 - 0x30 456F | Channel 6 Parameter Registers         |

| 0x30 4170 - 0x30 417F<br>0x30 4570 - 0x30 457F | Channel 7 Parameter Registers         |

| 0x30 4180 - 0x30 418F<br>0x30 4580 - 0x30 458F | Channel 8 Parameter Registers         |

| 0x30 4190 - 0x30 419F<br>0x30 4590 - 0x30 459F | Channel 9 Parameter Registers         |

| 0x30 41A0 - 0x30 41AF<br>0x30 45A0 - 0x30 45AF | Channel 10 Parameter Registers        |

| 0x30 41B0 - 0x30 41BF<br>0x30 45B0 - 0x30 45BF | Channel 11 Parameter Registers        |

| 0x30 41C0 - 0x30 41CF<br>0x30 45C0 - 0x30 45CF | Channel 12 Parameter Registers        |

| 0x30 41D0 – 0x30 41DF<br>0x30 45D0 – 0x30 45DF | Channel 13 Parameter Registers        |

| 0x30 41E0 - 0x30 41EF<br>0x30 45E0 - 0x30 45EF | Channel 14 Parameter Registers        |

| 0x30 41F0 - 0x30 41FF<br>0x30 45F0 - 0x30 45FF | Channel 15 Parameter Registers        |

# 17.4.1 TPU Module Configuration Register

# **TPUMCR** — TPU Module Configuration Register

0x30 4000 0x30 4400

| MSB    |     |     |     |     |     |      |     |      |      |      |       |    |      |      | LSB |

|--------|-----|-----|-----|-----|-----|------|-----|------|------|------|-------|----|------|------|-----|

| 0      | 1   | 2   | 3   | 4   | 5   | 6    | 7   | 8    | 9    | 10   | 11    | 12 | 13   | 14   | 15  |

| STOP   | TCF | R1P | TCF | R2P | EMU | T2CG | STF | SUPV | PSCK | TPU3 | T2CSL |    | RESE | RVED |     |

| RESET: |     |     |     |     |     |      |     |      |      |      |       |    |      |      |     |

| 0      | 0   | 0   | 0   | 0   | 0   | 0    | 0   | 1    | 0    | 1    | 0     | 0  | 0    | 0    | 0   |

# **Table 17-6 TPUMCR Bit Settings**

| Bit(s) | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | STOP  | Low-power stop mode enable. If the STOP bit in TPUMCR is set, the TPU3 shuts down its internal clocks, shutting down the internal microengine. TCR1 and TCR2 cease to increment and retain the last value before the stop condition was entered. The TPU3 asserts the stop flag (STF) in TPUMCR to indicate that it has stopped.  0 = Enable TPU3 clocks 1 = Disable TPU3 clocks                                                                                                                                                         |

| 1:2    | TCR1P | Timer count register 1 prescaler control. TCR1 is clocked from the output of a prescaler. The prescaler divides its input by 1, 2, 4, or 8. This is a write-once field unless the PWOD bit in TPUMCR3 is set.  00 = Divide by 1  01 = Divide by 2  10 = Divide by 4  11 = Divide by 8                                                                                                                                                                                                                                                    |

|        |       | Refer to 17.3.8 Prescaler Control for TCR1 for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3:4    | TCR2P | Timer count register 2 prescaler control. TCR2 is clocked from the output of a prescaler. The prescaler divides this input by 1, 2, 4, or 8. This is a write-once field unless the PWOD bit in TPUMCR3 is set.  00 = Divide by 1 01 = Divide by 2 10 = Divide by 4 11 = Divide by 8 Refer to 17.3.9 Prescaler Control for TCR2 for more information.                                                                                                                                                                                     |

| 5      | EMU   | Emulation control. In emulation mode, the TPU3 executes microinstructions from DPTRAM exclusively. Access to the DPTRAM via the IMB3 is blocked, and the DPTRAM is dedicated for use by the TPU3. After reset, this bit can be written only once.  0 = TPU3 and DPTRAM operate normally 1 = TPU3 and DPTRAM operate in emulation mode                                                                                                                                                                                                    |

| 6      | T2CG  | TCR2 clock/gate control 0 = TCR2 pin used as clock source for TCR2 1 = TCR2 pin used as gate of DIV8 clock for TCR2 Refer to 17.3.9 Prescaler Control for TCR2 for more information.                                                                                                                                                                                                                                                                                                                                                     |

| 7      | STF   | Stop flag. 0 = TPU3 is operating normally 1 = TPU3 is stopped (STOP bit has been set)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8      | SUPV  | Supervisor data space 0 = Assignable registers are accessible from user or supervisor privilege level 1 = Assignable registers are accessible from supervisor privilege level only                                                                                                                                                                                                                                                                                                                                                       |

| 9      | PSCK  | Standard prescaler clock. Note that this bit has no effect if the extended prescaler is selected (EPSCKE = 1).  0 = fSYS ÷ 32 is input to TCR1 prescaler, if standard prescaler is selected  1 = fSYS ÷ 4 is input to TCR1 prescaler, if standard prescaler is selected                                                                                                                                                                                                                                                                  |

| 10     | TPU3  | TPU3 enable. The TPU3 enable bit provides compatibility with the TPU. If running TPU code on the TPU3, the microcode size should not be greater than 2 Kbytes and the TPU3 enable bit should be cleared to zero. The TPU3 enable bit is write-once after reset. The reset value is one, meaning that the TPU3 will operate in TPU3 mode.  0 = TPU mode; zero is the TPU reset value 1 = TPU3 mode; one is the TPU3 reset value  NOTE: The programmer should not change this value unless necessary when developing custom TPU microcode. |

| 11     | T2CSL | TCR2 counter clock edge. This bit and the T2CG control bit determine the clock source for TCR2. Refer to 17.3.9 Prescaler Control for TCR2 for details.                                                                                                                                                                                                                                                                                                                                                                                  |

| 12:15  | _     | Reserved. These bits are used for the IARB (interrupt arbitration ID) field in TPU3 implementations that use hardware interrupt arbitration.                                                                                                                                                                                                                                                                                                                                                                                             |

# 17.4.2 TPU3 Test Configuration Register

0x30 4002, 0x30 4402

**TCR** — TPU3 Test Configuration Register Used for factory test only.

17.4.3 Development Support Control Register

| DSCR   | R — D | evelo | pment | t Sup <sub>l</sub> | oort C | ontrol | Reg | ister |     |    |    |    |    | x30 4<br>x30 4 |     |

|--------|-------|-------|-------|--------------------|--------|--------|-----|-------|-----|----|----|----|----|----------------|-----|

| MSB    |       |       |       |                    |        |        |     |       |     |    |    |    |    |                | LSB |

| 0      | 1     | 2     | 3     | 4                  | 5      | 6      | 7   | 8     | 9   | 10 | 11 | 12 | 13 | 14             | 15  |

| НОТ4   |       | RESE  | RVED  |                    | BLC    | CLKS   | F   | RZ    | CCL | BP | ВС | ВН | BL | BM             | ВТ  |

| RESET: |       |       |       |                    |        |        |     |       |     |    |    |    |    |                |     |

0

# Table 17-7 DSCR Bit Settings

| Bit(s) | Name | Description                                                                                                                                                                                                                                                                                                                                                                     |

|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | НОТ4 | Hang on T4 0 = Exit wait on T4 state caused by assertion of HOT4 1 = Enter wait on T4 state                                                                                                                                                                                                                                                                                     |

| 1:4    | _    | Reserved                                                                                                                                                                                                                                                                                                                                                                        |

| 5      | BLC  | Branch latch control  0 = Latch conditions into branch condition register before exiting halted state  1 = Do not latch conditions into branch condition register before exiting the halted state or during the time-slot transition period                                                                                                                                     |

| 6      | CLKS | Stop clocks (to TCRs) 0 = Do not stop TCRs 1 = Stop TCRs during the halted state                                                                                                                                                                                                                                                                                                |

| 7:8    | FRZ  | FREEZE assertion response. The FRZ bits specify the TPU microengine response to the IMB3 FREEZE signal 00 = Ignore freeze 01 = Reserved 10 = Freeze at end of current microcycle 11 = Freeze at next time-slot boundary                                                                                                                                                         |

| 9      | CCL  | Channel conditions latch. CCL controls the latching of channel conditions (MRL and TDL) when the CHAN register is written.  0 = Only the pin state condition of the new channel is latched as a result of the write CHAN register microinstruction  1 = Pin state, MRL, and TDL conditions of the new channel are latched as a result of a write CHAN register microinstruction |

| 10     | BP   | $\mu$ PC breakpoint enable 0 = Breakpoint not enabled 1 = Break if $\mu$ PC equals $\mu$ PC breakpoint register                                                                                                                                                                                                                                                                 |

| 11     | ВС   | Channel breakpoint enable  0 = Breakpoint not enabled  1 = Break if CHAN register equals channel breakpoint register at beginning of state or when CHAN is changed through microcode                                                                                                                                                                                            |

| 12     | ВН   | Host service breakpoint enable  0 = Breakpoint not enabled  1 = Break if host service latch is asserted at beginning of state                                                                                                                                                                                                                                                   |

| 13     | BL   | Link service breakpoint enable  0 = Breakpoint not enabled  1 = Break if link service latch is asserted at beginning of state                                                                                                                                                                                                                                                   |

| 14     | BM   | MRL breakpoint enable 0 = Breakpoint not enabled 1 = Break if MRL is asserted at beginning of state                                                                                                                                                                                                                                                                             |

| 15     | ВТ   | TDL breakpoint enable 0 = Breakpoint not enabled 1 = Break if TDL is asserted at beginning of state                                                                                                                                                                                                                                                                             |

# 17.4.4 Development Support Status Register

# **DSSR** — Development Support Status Register

0x30 4006 0x30 4406

| MSB    |   |   |      |      |   |   |   |      |      |      |      |      |    |        | LSB |

|--------|---|---|------|------|---|---|---|------|------|------|------|------|----|--------|-----|

| 0      | 1 | 2 | 3    | 4    | 5 | 6 | 7 | 8    | 9    | 10   | 11   | 12   | 13 | 14     | 15  |

|        |   |   | RESE | RVED |   |   |   | BKPT | PCBK | СНВК | SRBK | TPUF | RI | ESERVE | D   |

| RESET: |   |   |      |      |   |   |   |      |      |      |      |      |    |        |     |

| 0      | 0 | 0 | 0    | 0    | 0 | 0 | 0 | 0    | 0    | 0    | 0    | 0    | 0  | 0      | 0   |

#### **Table 17-8 DSSR Bit Settings**

| Bit(s) | Name | Description                                                                                                                                                                                                                                                                               |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:7    | _    | Reserved                                                                                                                                                                                                                                                                                  |

| 8      | BKPT | Breakpoint asserted flag. If an internal breakpoint caused the TPU3 to enter the halted state, the TPU3 asserts the BKPT signal on the IMB and sets the BKPT flag. BKPT remains set until the TPU3 recognizes a breakpoint acknowledge cycle, or until the IMB FREEZE signal is asserted. |

| 9      | PCBK | $\mu PC$ breakpoint flag. PCBK is asserted if a breakpoint occurs because of a $\mu PC$ (microprogram counter) register match with the $\mu PC$ breakpoint register. PCBK is negated when the BKPT flag is cleared.                                                                       |

| 10     | СНВК | Channel register breakpoint flag. CHBK is asserted if a breakpoint occurs because of a CHAN register match with the CHAN register breakpoint register. CHBK is negated when the BKPT flag is cleared.                                                                                     |

| 11     | SRBK | Service request breakpoint flag. SRBK is asserted if a breakpoint occurs because of any of the service request latches being asserted along with their corresponding enable flag in the development support control register. SRBK is negated when the BKPT flag is cleared.              |

| 12     | TPUF | TPU3 FREEZE flag. TPUF is set whenever the TPU3 is in a halted state as a result of FREEZE being asserted. This flag is automatically negated when the TPU3 exits the halted state because of FREEZE being negated.                                                                       |

| 13:15  | _    | Reserved                                                                                                                                                                                                                                                                                  |

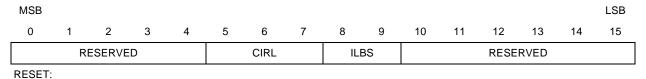

# 17.4.5 TPU3 Interrupt Configuration Register

TICR — TPU3 Interrupt Configuration Register

0x30 4008 0x30 4408

0 0 0 0 0 0 0

#### Table 17-9 TICR Bit Settings

| Bit(s) | Name | Description                                                                                                                                                                                                                                                                                        |

|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:4    | _    | Reserved                                                                                                                                                                                                                                                                                           |

| 5:7    | CIRL | Channel interrupt request level. This three-bit field specifies the interrupt request level for all channels. T field is used in conjunction with the ILBS field to determine the request level of TPU3 interrupts.                                                                                |

| 8:9    | ILBS | Interrupt level byte select. This field and the CIRL field determine the level of TPU3 interrupt requests. $00 = \overline{IRQ[0:7]} \text{ selected} \\ 01 = \overline{IRQ[8:15]} \text{ selected} \\ 10 = \overline{IRQ[16:23]} \text{ selected} \\ 11 = \overline{IRQ[24:31]} \text{ selected}$ |

| 10:15  | -    | Reserved. Note that bits 10:11 represent channel interrupt base vector (CIBV) bits in some TPU3 implementations.                                                                                                                                                                                   |

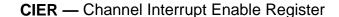

#### 17.4.6 Channel Interrupt Enable Register

The channel interrupt enable register (CIER) allows the CPU to enable or disable the ability of individual TPU3 channels to request interrupt service. Setting the appropriate bit in the register enables a channel to make an interrupt service request; clearing a bit disables the interrupt.

0x30 400A 0x30 440A

#### **Table 17-10 CIER Bit Settings**

| Bit(s) | Name     | Description                                                                                                              |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------|

| 0:15   | CH[15:0] | Channel interrupt enable/disable 0 = Channel interrupts disabled 1 = Channel interrupts enabled                          |

|        |          | <b>Note:</b> The MSB (bit 0 in big-endian mode) represents CH15, and the LSB (bit 15 in big-endian mode) represents CH0. |

# 17.4.7 Channel Function Select Registers

Encoded 4-bit fields within the channel function select registers specify one of 16 time functions to be executed on the corresponding channel. Encodings for predefined functions will be provided in a subsequent draft of this document.

| CFSR  | RO — | Chan | nel Fı | unctio | n Sel  | ect Re         | egiste | r 0 |    |                |    |    |    |    | 400C<br>440C |

|-------|------|------|--------|--------|--------|----------------|--------|-----|----|----------------|----|----|----|----|--------------|

| MSB   |      |      |        |        |        |                |        |     |    |                |    |    |    |    | LSB          |

| 0     | 1    | 2    | 3      | 4      | 5      | 6              | 7      | 8   | 9  | 10             | 11 | 12 | 13 | 14 | 15           |

|       | CH   | l 15 |        |        | СН     | l 14           |        |     | СН | 13             |    |    | СН | 12 |              |

| RESET | :    |      |        |        |        |                |        |     |    |                |    |    |    |    |              |

| 0     | 0    | 0    | 0      | 0      | 0      | 0              | 0      | 0   | 0  | 0              | 0  | 0  | 0  | 0  | 0            |

| CFSR  | R1 — | Chan | nel Fı | unctio | n Sele | ect Re         | egiste | r 1 |    |                |    |    |    |    | 400E<br>440E |

| MSB   |      |      |        |        |        |                |        |     |    |                |    |    |    |    | LSB          |

| 0     | 1    | 2    | 3      | 4      | 5      | 6              | 7      | 8   | 9  | 10             | 11 | 12 | 13 | 14 | 15           |

|       | CH   | 111  |        |        | CH     | I 10           |        |     | Cl | <del>1</del> 9 |    |    | CH | 18 |              |

| RESET | :    |      |        |        |        |                |        | •   |    |                |    |    |    |    |              |

| 0     | 0    | 0    | 0      | 0      | 0      | 0              | 0      | 0   | 0  | 0              | 0  | 0  | 0  | 0  | 0            |

| CFSR  | R2 — | Chan | nel Fı | unctio | n Sel  | ect Re         | egiste | r 2 |    |                |    |    |    |    | 4010<br>4410 |

| MSB   |      |      |        |        |        |                |        |     |    |                |    |    |    |    | LSB          |

| 0     | 1    | 2    | 3      | 4      | 5      | 6              | 7      | 8   | 9  | 10             | 11 | 12 | 13 | 14 | 15           |

|       | CI   | H 7  |        |        | Cł     | <del>1</del> 6 |        |     | CH | <del>1</del> 5 |    |    | CH | 14 |              |

| RESET | :    |      |        |        |        |                |        |     |    |                |    |    |    |    |              |

| 0     | 0    | 0    | 0      | 0      | 0      | 0              | 0      | 0   | 0  | 0              | 0  | 0  | 0  | 0  | 0            |

| CFSR  | R3 — | Chan | nel Fı | unctio | n Sel  | ect Re         | egiste | r 3 |    |                |    |    | _  |    | 4012<br>4412 |

| MSB   |      |      |        |        |        |                |        |     |    |                |    |    |    |    | LSB          |

| 0     | 1    | 2    | 3      | 4      | 5      | 6              | 7      | 8   | 9  | 10             | 11 | 12 | 13 | 14 | 15           |

# **Table 17-11 CFSRx Bit Settings**

0

CH 1

CH 2

0

| Name      | Description                                                                                         |

|-----------|-----------------------------------------------------------------------------------------------------|

| CH[15:0]  | Encoded time function for each channel. Encoded four-bit fields in the channel function select reg- |

| Cri[13.0] | isters specify one of 16 time functions to be executed on the corresponding channel.                |

#### 17.4.8 Host Sequence Registers

CH 3

RESET:

The host sequence field selects the mode of operation for the time function selected on a given channel. The meaning of the host sequence bits depends on the time function specified. Meanings of host sequence bits and host service request bits for predefined time functions will be provided in a subsequent draft of this document.

CH 0

0

0x30 4014 0x30 4414

|        |      |      |      |      |       |       |    |    |    |    |      |    |                | 7.00   |     |

|--------|------|------|------|------|-------|-------|----|----|----|----|------|----|----------------|--------|-----|

| MSB    |      |      |      |      |       |       |    |    |    |    |      |    |                |        | LSB |

| 0      | 1    | 2    | 3    | 4    | 5     | 6     | 7  | 8  | 9  | 10 | 11   | 12 | 13             | 14     | 15  |

| СН     | 15   | СН   | l 14 | СН   | 13    | СН    | 12 | СН | 11 | СН | I 10 | CI | <del>1</del> 9 | CH     | H 8 |

| RESET: |      |      |      |      |       |       |    |    |    |    |      |    |                |        |     |

| 0      | 0    | 0    | 0    | 0    | 0     | 0     | 0  | 0  | 0  | 0  | 0    | 0  | 0              | 0      | 0   |

| HSQF   | R1 — | Host | Sequ | ence | Regis | ter 1 |    |    |    |    |      |    |                | )x30 4 |     |

| MSB    |      |      |      |      |       |       |    |    |    |    |      |    |                |        | LSB |

| 0      | 1    | 2    | 3    | 4    | 5     | 6     | 7  | 8  | 9  | 10 | 11   | 12 | 13             | 14     | 15  |

| СН     | 17   | CH   | 16   | CH   | l 5   | CH    | 14 | CH | 13 | Cł | 12   | CI | <del> </del> 1 | CH     | H 0 |

| RESET: |      |      |      | -    |       | •     |    | •  |    | •  |      | •  |                | -      |     |

# Table 17-12 HSQRx Bit Settings

| Name     | Description                                                                                                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH[15:0] | Encoded host sequence. The host sequence field selects the mode of operation for the time function selected on a given channel. The meaning of the host sequence bits depends on the time function specified. |

#### 17.4.9 Host Service Request Registers

The host service request field selects the type of host service request for the time function selected on a given channel. The meaning of the host service request bits is determined by time function microcode. Refer to the *TPU Reference Manual* (TPURM/AD) and the Motorola TPU Literature Package (TPULITPAK/D) for more information.

| HSRF   | R0 — | Host | Servi | ce Re | quest | Regi | ster 0 |    |    |    |    |    |    | )x30 4<br>)x30 4 |     |

|--------|------|------|-------|-------|-------|------|--------|----|----|----|----|----|----|------------------|-----|

| MSB    |      |      |       |       |       |      |        |    |    |    |    |    |    |                  | LSB |

| 0      | 1    | 2    | 3     | 4     | 5     | 6    | 7      | 8  | 9  | 10 | 11 | 12 | 13 | 14               | 15  |

| СН     | 15   | СН   | 14    | СН    | 13    | СН   | 12     | СН | 11 | СН | 10 | CH | 19 | CH               | 18  |

| RESET: |      |      |       |       |       |      |        |    |    |    |    |    |    |                  |     |

| 0      | 0    | 0    | 0     | 0     | 0     | 0    | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0                | 0   |

| MSB    |    |    |                |    |                |    |                |    |                |    |    |    |                |    | LSB |

|--------|----|----|----------------|----|----------------|----|----------------|----|----------------|----|----|----|----------------|----|-----|

| 0      | 1  | 2  | 3              | 4  | 5              | 6  | 7              | 8  | 9              | 10 | 11 | 12 | 13             | 14 | 15  |

| CH     | 17 | CH | <del>1</del> 6 | CI | <del>1</del> 5 | CI | <del>1</del> 4 | Cl | <del>1</del> 3 | CH | 12 | CH | <del>1</del> 1 | CI | H 0 |

| RESET: | •  |    |                |    |                |    |                |    |                |    |    |    |                |    |     |

| 0      | 0  | 0  | 0              | 0  | 0              | 0  | 0              | 0  | 0              | 0  | 0  | 0  | 0              | 0  | 0   |

# **Table 17-13 HSSRx Bit Settings**

| Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Encoded type of host service. The host service request field selects the type of host service request for the time function selected on a given channel. The meaning of the host service request bits depends on the time function specified.                                                                                                                                                                                                                |

| CH[15:0] | A host service request field cleared to 0b00 signals the host that service is completed by the microengine on that channel. The host can request service on a channel by writing the corresponding host service request field to one of three non-zero states. The CPU must monitor the host service request register until the TPU3 clears the service request to 0b00 before any parameters are changed or a new service request is issued to the channel. |

# 17.4.10 Channel Priority Registers

The channel priority registers (CPR1, CPR2) assign one of three priority levels to a channel or disable the channel.

#### **CPR0** — Channel Priority Register 0

0x30 401C 0x30 441C

|   | MSB    |    |    |    |    |      |    |    |    |      |    |      |    |                |    | LSB |

|---|--------|----|----|----|----|------|----|----|----|------|----|------|----|----------------|----|-----|

|   | 0      | 1  | 2  | 3  | 4  | 5    | 6  | 7  | 8  | 9    | 10 | 11   | 12 | 13             | 14 | 15  |

|   | СН     | 15 | СН | 14 | CH | l 13 | СН | 12 | CH | l 11 | CH | l 10 | CH | <del>1</del> 9 | CI | H 8 |

| _ | RESET: |    |    |    |    |      |    |    |    |      |    |      |    |                |    |     |

|   | 0      | 0  | 0  | 0  | 0  | 0    | 0  | 0  | 0  | 0    | 0  | 0    | 0  | 0              | 0  | 0   |

#### **CPR1** — Channel Priority Register 1

0x30 401E 0x30 441E

| MSB    |    |    |                |    |                |    |                |    |                |    |    |    |    |    | LSB |

|--------|----|----|----------------|----|----------------|----|----------------|----|----------------|----|----|----|----|----|-----|

| 0      | 1  | 2  | 3              | 4  | 5              | 6  | 7              | 8  | 9              | 10 | 11 | 12 | 13 | 14 | 15  |

| СН     | 17 | CH | <del>1</del> 6 | CH | <del>1</del> 5 | CH | <del> </del> 4 | CH | <del>1</del> 3 | CH | 12 | CH | 11 | CI | H 0 |

| RESET: |    |    |                |    |                |    |                |    |                |    |    |    |    |    |     |

| 0      | 0  | 0  | 0              | 0  | 0              | 0  | 0              | 0  | 0              | 0  | 0  | 0  | 0  | 0  | 0   |

# **Table 17-14 CPRx Bit Settings**

| Name     | Description                                                                                         |

|----------|-----------------------------------------------------------------------------------------------------|

| CH[15:0] | Encoded channel priority levels. Table 17-15 indicates the number of time slots guaranteed for each |

| CH[15.0] | channel priority encoding.                                                                          |

| Г |    |   |   |  |

|---|----|---|---|--|

| ı | 'n | П |   |  |

| ı |    | J |   |  |

|   |    |   | 4 |  |

| CHx[1:0] | Service  | Guaranteed Time Slots |

|----------|----------|-----------------------|

| 00       | Disabled | _                     |

| 01       | Low      | 1 out of 7            |

| 10       | Middle   | 2 out of 7            |

| 11       | High     | 4 out of 7            |

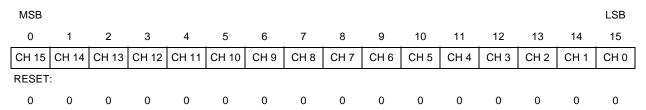

#### 17.4.11 Channel Interrupt Status Register

The channel interrupt status register (CISR) contains one interrupt status flag per channel. Time functions specify via microcode when an interrupt flag is set. Setting a flag causes the TPU3 to make an interrupt service request if the corresponding CIER bit is set. To clear a status flag, read CISR, then write a zero to the appropriate bit. CISR is the only TPU3 register that can be accessed on a byte basis.

**Table 17-16 CISR Bit Settings**

| Bit(s) | Name     | Description                                                                                |  |  |  |

|--------|----------|--------------------------------------------------------------------------------------------|--|--|--|

| 0:15   | CH[15:0] | Channel interrupt status 0 = Channel interrupt not asserted 1 = Channel interrupt asserted |  |  |  |

#### 17.4.12 Link Register

LR — Link Register 0x30 4022, 0x30 4422

Used for factory test only.

#### 17.4.13 Service Grant Latch Register

SGLR — Service Grant Latch Register 0x30 4024, 0x30 4424 Used for factory test only.

#### 17.4.14 Decoded Channel Number Register

DCNR — Decoded Channel Number RegisterUsed for factory test only.

# 17.4.15 TPU3 Module Configuration Register 2

# **TPUMCR2** — TPU Module Configuration Register 2

MSB LSB 0 1 5 6 7 8 10 11 12 13 14 15 SOFT DIV2 ETBANK **FPSCK** T2CF DTPU RESERVED RST RESET: 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

# Table 17-17 TPUMCR2 Bit Settings

| Bit(s) | Name                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0:6    | _                                           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 7      | DIV2                                        | Divide by 2 control. When asserted, the DIV2 bit, along with the TCR1P bit and the PSCK bit in the TPUMCR, determines the rate of the TCR1 counter in the TPU3. If set, the TCR1 counter increments at a rate of two system clocks. If negated, TCR1 increments at the rate determined by control bits in the TCR1P and PSCK fields.  0 = TCR1 increments at rate determined by control bits in the TCR1P and PSCK fields of the TPUMCR register  1 = Causes TCR1 counter to increment at a rate of the system clock divided by two |  |

| 8      | 1 = Puts TPU3 in reset until bit is cleared |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|        |                                             | <b>NOTE</b> : Do not attempt to access any other TPU3 registers when this bit is asserted. When this bit is asserted, it is the only accessible bit in the register.                                                                                                                                                                                                                                                                                                                                                                |  |

| 9:10   | ETBANK                                      | Entry table bank select. This field determines the bank where the microcoded entry table is situated. After reset, this field is %00. This control bit field is write once after reset. ETBANK is used when the microcode contains entry tables not located in the default bank 0. To execute the ROM functions on this MCU, ETBANK[1:0] must be 00. Refer to Table 17-18.                                                                                                                                                          |  |

|        |                                             | <b>NOTE</b> : This field should not be modified by the programmer unless necessary because of custom microcode.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 11:13  | FPSCK                                       | Filter prescaler clock. The filter prescaler clock control bit field determines the ratio between system clock frequency and minimum detectable pulses. The reset value of these bits is zero, defining the filter clock as four system clocks. Refer to <b>Table 17-19</b> .                                                                                                                                                                                                                                                       |  |

| 14     | T2CF                                        | T2CLK pin filter control. When asserted, the T2CLK input pin is filtered with the same filter clock that is supplied to the channels. This control bit is write once after reset.  0 = Uses fixed four-clock filter  1 = T2CLK input pin filtered with same filter clock that is supplied to the channels                                                                                                                                                                                                                           |  |

| 15     | DTPU                                        | Disable TPU3 pins. When the disable TPU3 control pin is asserted, pin TP15 is configured as an input disable pin. When the TP15 pin value is zero, all TPU3 output pins are three-stated, regardless of the pins function. The input is not synchronized. This control bit is write once after reset.  0 = TP15 functions as normal TPU3 channel 1 = TP15 pin configured as output disable pin. When TP15 pin is low, all TPU3 output pins are in a high-impedance state, regardless of the pin function.                           |  |

| ETBANK | Bank |

|--------|------|

| 00     | 0    |

| 01     | 1    |

| 10     | 2    |

| 11     | 3    |

# **Table 17-19 System Clock Frequency/Minimum Guaranteed Detected Pulse**

| Filter Control | Divide By | 20 MHz  | 33 MHz   | 40 MHz   |  |

|----------------|-----------|---------|----------|----------|--|

| 000            | 4         | 200 ns  | 121 ns   | 100 ns   |  |

| 001            | 8         | 400 ns  | 242 ns   | 200 ns   |  |

| 010            | 16        | 800 ns  | 485 ns   | 400 ns   |  |

| 011            | 32        | 1.6 μs  | 970 ns   | 800 ns   |  |

| 100            | 64        | 3.2 μs  | 1.94 μs  | 1.60 μs  |  |

| 101            | 128       | 6.4 μs  | 3.88 μs  | 3.20 μs  |  |

| 110            | 256       | 12.8 μs | 7.76 µs  | 6.40 μs  |  |

| 111            | 512       | 25.6 μs | 15.51 μs | 12.80 μs |  |

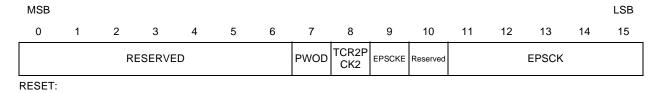

# 17.4.16 TPU Module Configuration Register 3

**TPUMCR3** — TPU Module Configuration Register 3

0x30 402A 0x30 442A

# Table 17-20 TPUMCR3 Bit Settings

0

0

| Bit(s) | Name          | Description                                                                                                                                                                                     |

|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:6    | _             | Reserved                                                                                                                                                                                        |

| 7      | PWOD          | Prescaler write-once disable bit. The PWOD bit does not lock the EPSCK field and the EPSCKE bit.  0 = Prescaler fields in MCR are write-once 1 = Prescaler fields in MCR can be written anytime |

| 8      | TCR2PSC<br>K2 | TCR2 prescaler 2 0 = Prescaler clock source is divided by one. 1 = Prescaler clock is divided. See divider definitions in <b>Table 17-4</b> .                                                   |

| 9      | EPSCKE        | Enhanced pre-scaler enable  0 = Disable enhanced prescaler (use standard prescaler)  1 = Enable enhanced prescaler. System clock will be divided by the value in EPSCK field.                   |

| 10     | _             | Reserved                                                                                                                                                                                        |

| 11:15  | EPSCK         | Enhanced prescaler value that will be loaded into the enhanced prescaler counter. Prescaler value = (EPSCK + 1) x 2. Refer to 17.3.8 Prescaler Control for TCR1 for details.                    |

#### 17.4.17 TPU3 Test Registers

The following TPU3 registers are used for factory test only:

- Internal Scan Data Register (ISDR, address offset 0x30 402A, 0x30 442A)

- Internal Scan Control Register (ISCR, address offset 0x30 402E, 0x30 442E)

#### 17.4.18 TPU3 Parameter RAM

The channel parameter registers are organized as one hundred 16-bit words of RAM. Channels 0 to 15 have eight parameters. The parameter registers constitute a shared work space for communication between the CPU and the TPU3. The TPU3 can only access data in the parameter RAM. Refer to **Table 17-21**.

Table 17-21 Parameter RAM Address Offset Map<sup>1</sup>

| Channel | Parameter  |            |            |            |            |            |            |            |

|---------|------------|------------|------------|------------|------------|------------|------------|------------|

| Number  | 0          | 1          | 2          | 3          | 4          | 5          | 6          | 7          |

| 0       | 100        | 102        | 104        | 106        | 108        | 10A        | 10C        | 10E        |

| O       | 500        | 502        | 504        | 506        | 508        | 50A        | 50C        | 50E        |

| 1       | 110        | 112        | 114        | 116        | 118        | 11A        | 11C        | 11E        |

| '       | 510        | 512        | 514        | 516        | 518        | 51A        | 51C        | 51E        |

| 2       | 120        | 122        | 124        | 126        | 128        | 12A        | 12C        | 12E        |

|         | 520        | 522        | 524        | 526        | 528        | 52A        | 52C        | 52E        |

| 3       | 130        | 132        | 134        | 136        | 138        | 13A        | 13C        | 13E        |

| _       | 530        | 532        | 534        | 536        | 538        | 53A        | 53C        | 53E        |

| 4       | 140        | 142        | 144        | 146        | 148        | 14A        | 14C        | 14E        |

|         | 540        | 542        | 544        | 546        | 548        | 54A        | 54C        | 54C        |

| 5       | 150        | 152        | 154        | 156        | 158        | 15A        | 15C        | 15E        |

|         | 550        | 552        | 554        | 556        | 558        | 55A        | 55C        | 55E        |

| 6       | 160        | 162        | 164        | 166        | 168        | 16A        | 16C        | 16E        |

|         | 560        | 562        | 564        | 566        | 568        | 56A        | 56C        | 56E        |

| 7       | 170<br>570 | 172<br>572 | 174<br>574 | 176<br>576 | 178<br>578 | 17A<br>57A | 17C<br>57C | 17E<br>57E |

|         |            |            | 184        |            |            | 18A        |            | 18E        |

| 8       | 180<br>580 | 182<br>582 | 585        | 186<br>586 | 188<br>588 | 58A        | 18C<br>58C | 58E        |

|         | 190        | 192        | 194        | 196        | 198        | 19A        | 19C        | 19E        |

| 9       | 590        | 592        | 594        | 596        | 598        | 59A        | 59C        | 59E        |

|         | 1A0        | 1A2        | 1A4        | 1A6        | 1A8        | 1AA        | 1AC        | 1AE        |

| 10      | 5A0        | 5A2        | 5A4        | 5A6        | 5A8        | 5AA        | 5AC        | 5AE        |

| 4.4     | 1B0        | 1B2        | 1B4        | 1B6        | 1B8        | 1BA        | 1BC        | 1BE        |

| 11      | 5B0        | 5B2        | 5B4        | 5B6        | 5B8        | 5BA        | 5BC        | 5BE        |

| 40      | 1C0        | 1C2        | 1C4        | 1C6        | 1C8        | 1CA        | 1CC        | 1CE        |

| 12      | 5C0        | 5C2        | 5C4        | 5C6        | 5C8        | 5CA        | 5CC        | 5CE        |

| 13      | 1D0        | 1D2        | 1D4        | 1D6        | 1D8        | 1DA        | 1DC        | 1DE        |

|         | 5D0        | 5D2        | 5D4        | 5D6        | 5D8        | 5DA        | 5DC        | 5DE        |

| 14      | 1E0        | 1E2        | 1E4        | 1E6        | 1E8        | 1EA        | 1EC        | 1EE        |

| 14      | 5E0        | 5E2        | 5E4        | 5E6        | 5E8        | 5EA        | 5EC        | 5EE        |

| 15      | 1F0        | 1F2        | 1F4        | 1F6        | 1F8        | 1FA        | 1FC        | 1FE        |

|         | 5F0        | 5F2        | 5F4        | 5F6        | 5F8        | 5FA        | 5FC        | 5FE        |

NOTES:

<sup>1.</sup> These addresses should be added to 0x30 4000 to derive the complete parameter address.

# **17.5 Time Functions**

Descriptions of the MPC555 pre-programmed time functions are shown in Appendix D.