## SECTION 2 SIGNAL DESCRIPTIONS

## 2.1 Packaging and Pinout Descriptions

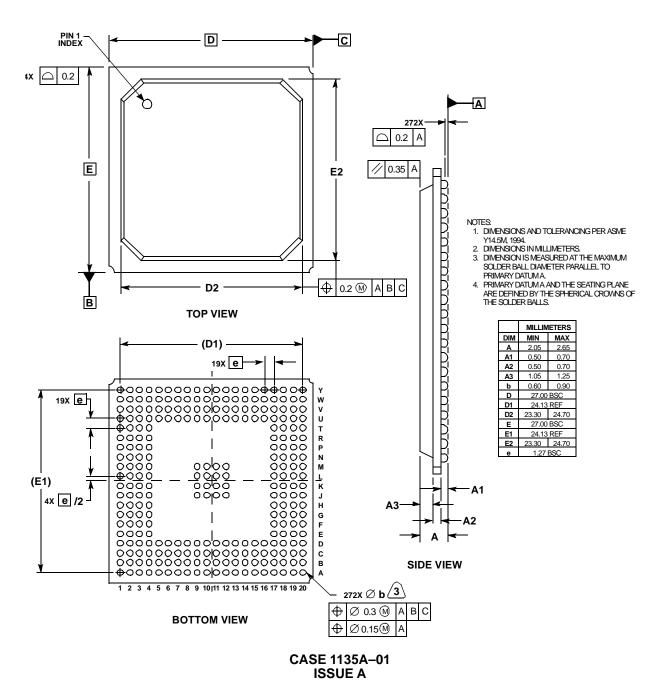

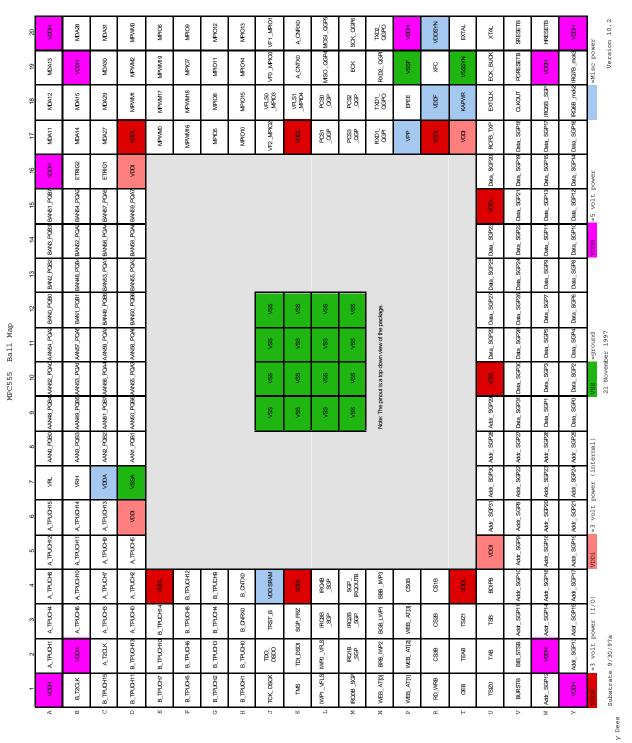

**Figure 2-1** gives the case configuration and packaging information for the MPC555. **Figure 2-2** gives the MPC555 pinout data. **Table 2-1** gives an overview of the pins on the MPC555.

Figure 2-1 MPC555 Case Dimensions and Packaging

Figure 2-2 MPC555 Pinout Data

| Functional Group                                 | Signals <sup>1</sup>                   | Pins | 3 V / 5 V <sup>2</sup> |

|--------------------------------------------------|----------------------------------------|------|------------------------|

| 24 Address lines<br>(16-Mbyte address space)     | ADDR[8:31]/SGPIOA[8:31]                | 24   | 3-V / 5-V GPIO         |

| 32-bit data bus                                  | DATA[0:31]/SGPIOD[0:31]                | 32   | 3-47 3-4 61 10         |

|                                                  | IRQ[0]/SGPIOC[0]                       |      |                        |

|                                                  | IRQ[1]/RSV/SGPIOC[1]                   |      |                        |

|                                                  | IRQ[2]/CR/SGPIOC[2]/MTS                |      |                        |

| External interrupts                              | IRQ[3]/KR/RETRY/SGPIOC[3]              | 8    | 3-V / 5-V GPIO         |

| ·                                                | IRQ[4]/AT[2]/SGPIOC[4]                 |      |                        |

|                                                  | IRQ[5]/SGPIOC[5]/MODCK[1] <sup>3</sup> |      |                        |

|                                                  | IRQ[6:7]/MODCK[2:3] <sup>3</sup>       |      |                        |

|                                                  | TSIZ[0:1]                              |      |                        |

|                                                  | RD/WR                                  |      |                        |

|                                                  | BURST                                  |      |                        |

|                                                  | BDIP                                   |      |                        |

|                                                  | TS                                     |      |                        |

| Bus control -                                    | TA                                     | 11   | 3 V                    |

|                                                  | TEA                                    |      |                        |

|                                                  | RSTCONF/TEXP <sup>3</sup>              |      |                        |

|                                                  | ŌĒ                                     |      |                        |

|                                                  | BI/STS                                 |      |                        |

| General purpose chip select machine              | <u>CS[0:3]</u>                         |      |                        |

| (multiplexed with development and debug support) | WE[0:3]/BE[0:3]/AT[0:3]                | 8    | 3 V                    |

| 5 ,                                              | PORESET <sup>3</sup>                   |      |                        |

| Power-on reset and reset                         | HRESET <sup>3</sup>                    | 3    | 3 V                    |

| configuration                                    | SRESET <sup>3</sup>                    |      |                        |

|                                                  | SGPIOC[6]/FRZ/PTR                      |      |                        |

|                                                  | SGPIOC[7]/IRQOUT/LWP[0]                |      |                        |

| Development and debug support                    | BG/VF[0]/LWP[1]                        | 5    | 3-V / 5-V GPIO         |

|                                                  | BR/VF[1]/IWP[2]                        |      |                        |

|                                                  | BB/VF[2]/IWP[3]                        |      |                        |

|                                                  | TMS                                    |      |                        |

|                                                  | TDI/DSDI                               |      |                        |

|                                                  | TCK/DSCK                               | _    | 2.1/                   |

| JTAG and debug port                              | TDO/DSDO                               | 7    | 3 V                    |

|                                                  | TRST                                   |      |                        |

|                                                  | IWP[0:1]/VFLS[0:1]                     |      |                        |

|                                                  | XTAL <sup>3</sup>                      |      |                        |

|                                                  | EXTAL <sup>3</sup>                     |      |                        |

|                                                  | CLKOUT                                 | 5    | 3 V                    |

| Clocks and PLL                                   | EXTCLK <sup>3</sup>                    |      |                        |

|                                                  | XFC                                    |      |                        |

|                                                  | ENGCLK/BUCLK                           | 1    | 5 V                    |

| Functional Group              | Signals <sup>1</sup>                                          | Pins | 3 V / 5 V <sup>2</sup> |  |

|-------------------------------|---------------------------------------------------------------|------|------------------------|--|

|                               | PCS0/<br>SS/QGPIO[0]<br>PCS[1:3]/QGPIO[1:3]                   |      |                        |  |

|                               | MISO/QGPIO[4]                                                 |      |                        |  |

| QSMCM                         | MOSI/QGPIO[5]                                                 | 12   | 5 V                    |  |

| gowow                         | SCK/QGPIO[6]                                                  | 12   |                        |  |

|                               | TXD[1:2]/QGPO[1:2]                                            |      |                        |  |

|                               | RXD[1:2]/QGPI[1:2]                                            |      |                        |  |

|                               | ECK                                                           |      |                        |  |

|                               | MDA[11], [13]                                                 |      |                        |  |

| MIOS                          | MDA[12], [14]                                                 | 18   | 5 V                    |  |

| MIOS                          | MDA[15], [27:31]                                              | 10   | 5 V                    |  |

|                               | MPWM[0:3], [16:19]                                            |      |                        |  |

|                               | VF[0:2]/MPIO32B[0:2]                                          | 5    | 3-V / 5-V GPIO         |  |

| General-Purpose I/O from MIOS | VFLS[0:1]/MPIO32B[3:4]                                        | 3    | 3-V / 3-V GFIO         |  |

|                               | MPIO32B[5:15]                                                 | 11   | 5 V                    |  |

| TPU                           | A_TPUCH[0:15], B_TPUCH[0:15]                                  | 34   | 5 V                    |  |

| 11 0                          | A_T2CLK, B_T2CLK                                              | 34   | 3 V                    |  |

|                               | ETRIG[1:2]                                                    |      |                        |  |

|                               | A_AN0/ANW/PQB0, B_AN0/ANW/PQB0                                |      |                        |  |

|                               | A_AN1/ANX/PQB1, B_AN1/ANX/PQB1                                |      |                        |  |

|                               | A_AN2/ANY/PQB2, B_AN2/ANY/PQB2                                |      |                        |  |

| QADC                          | A_AN3/ANZ/PQB3, B_AN3/ANZ/PQB3                                | 34   | 5 V                    |  |

|                               | A_AN[48:51]/PQB[4:7], B_AN[48:51]/PQB[4:7]                    |      |                        |  |

|                               | A_AN[52:54]/MA[0:2]/PQA[0:2],<br>B_AN[52:54]/MA[0:2]/PQA[0:2] |      |                        |  |

|                               | A_AN[55:56]/PQA[3:4], B_AN[55:56]/PQA[3:4]                    |      |                        |  |

|                               | A_AN[57:59]/PQA[5:7], B_AN[57:59]/PQA[5:7]                    |      |                        |  |

| TouCAN                        | A_CNTX0, B_CNTX0, A_CNRX0, B_CNRX0                            | 4    | 5 V                    |  |

| Flash EEPROM                  | E <sub>PEE</sub>                                              | 1    | 3 V                    |  |

|                               | Supplies                                                      |      |                        |  |

| Ground                        | VSS, VSSF, VSSSYN                                             | 18   |                        |  |

| Analog Ground                 | VSSA, VRL                                                     | 2    |                        |  |

| Low Voltage Supply            | VDDI, VDDL, VDDSRAM, VDDSYN, KAPWR <sup>3</sup> , VDDF        | 16   | 3 V                    |  |

| High voltage Supply           | VDDH, VDDA, VRH                                               | 12   | 5 V                    |  |

| Programming Voltage           | VPP                                                           | 1    | 3-V / 5-V              |  |

#### NOTES:

- 1. "/" implies that the corresponding functions are multiplexed on the pin

- 2. All inputs are 5 V friendly. All 5 V outputs are slow slew rate except for SCI transmit pins.

- 3. These pins are powered by KAPWR (Keep Alive Power Supply).

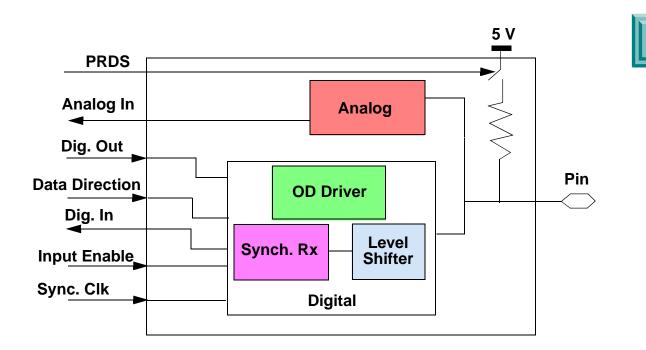

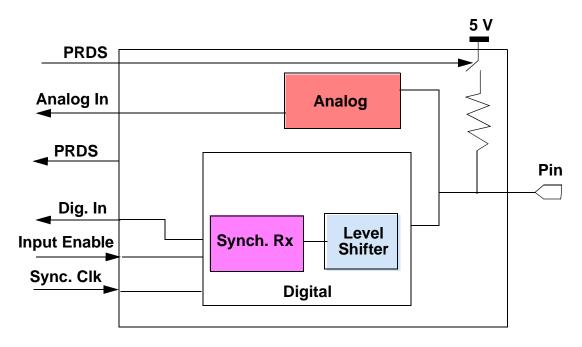

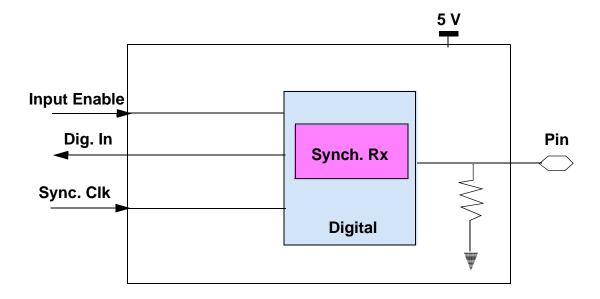

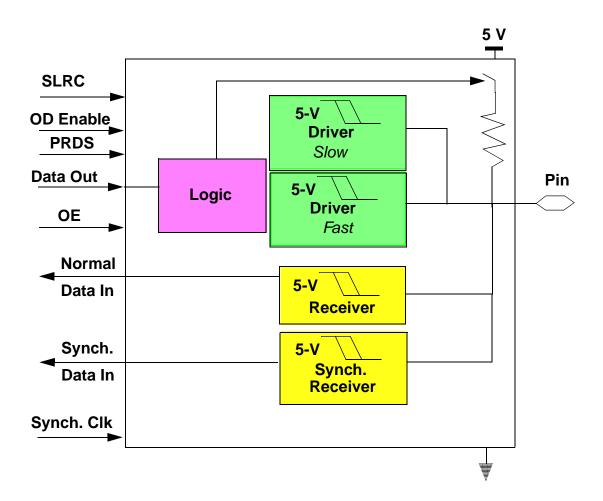

## 2.2 Pin Functionality

The pad ring supports 234 functional pins (284 including all power and ground). Some pins serve multiple functions. The pad characteristics for each pin are described in **Table 2-2**. This table contains the following columns:

Pin – List of functional (signal) names for each pin. (For actual pin names, see 2.7

Pin Names and Abbreviations.

- Function Name of function (signal). Each pin supports one or more functions, and each function (signal) name is a separate entry in the table.

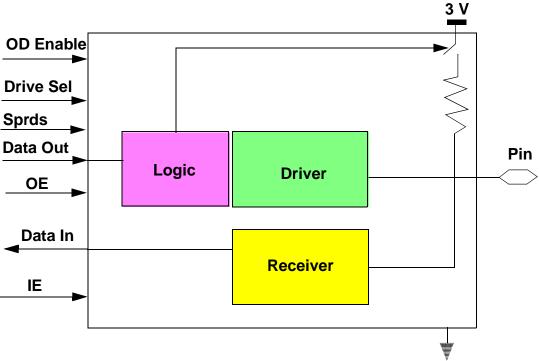

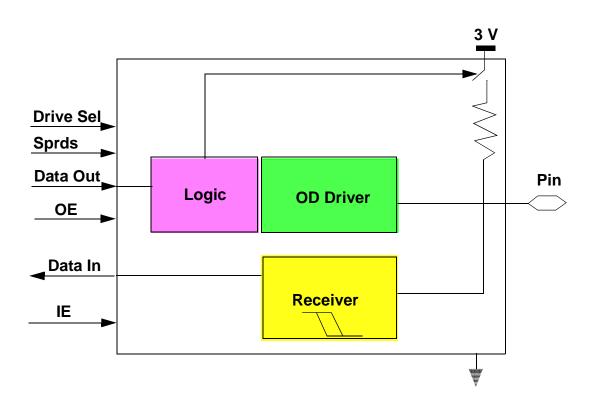

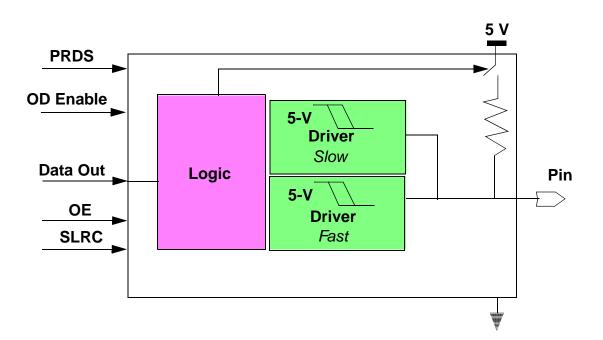

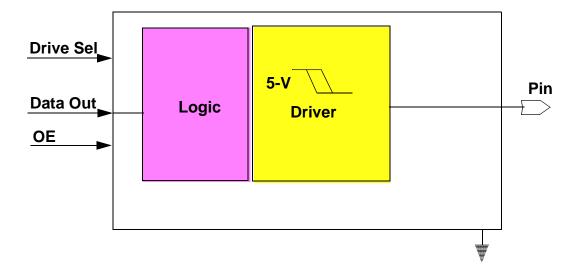

- Driver Type Type of driver that is used to drive the pin (for output functionality).

Types of output drivers are:

- Totem pole (TP). This driver type uses a push pull scheme to drive the pin. These pins can be driven high or low or can be three-stated. Care must be taken to ensure that there is no contention on this pin (for example, an external driver driving the pin high while an internal driver is driving it low).

- Open drain (OD). This driver type uses an open drain approach to drive the pins. Pins with an OD driver can be either driven low or three-stated. This driver scheme is typically used for pins that could potentially be asserted by multiple modules.

- Active negated (ANG). This driver type fully drives a low level. A high level is driven and then released. A pull-up resistor may be needed on this type of output.

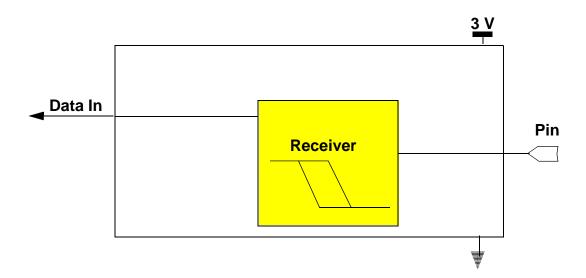

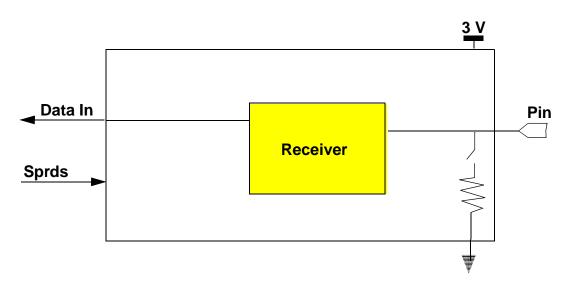

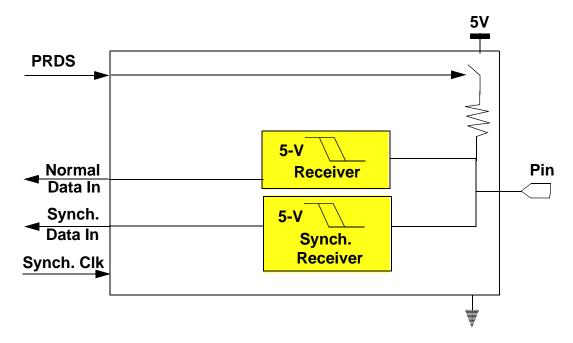

- Receiver Type Type of receiver used for the pin. Some inputs need to have a synchronizer to prevent latching a metastable signal at the pins. Such requirements are indicated in this column with the abbreviation "synch." Another possible entry is "glitch filter." It is added to reset signals.

- Direction Direction of the pin for each function it supports. The possible directions are input (I), output (O) and bi-directional (I/O).

- Voltage Voltage requirement for each function of a pin. There are two supply voltages: 5 V and 3 V.

- Slew rate Timing needed from the 5-V drivers. The options are with slew rate (typically 200/50 ns with 50 pF load) or fast 5-V driver.

- Drive strength Drive strength for 3-V drivers of the output load. For all 3-V outputs, the drive strength is 25/50 pF. For two pads (clkout and engclk) the drive strength is 45/90 pF.

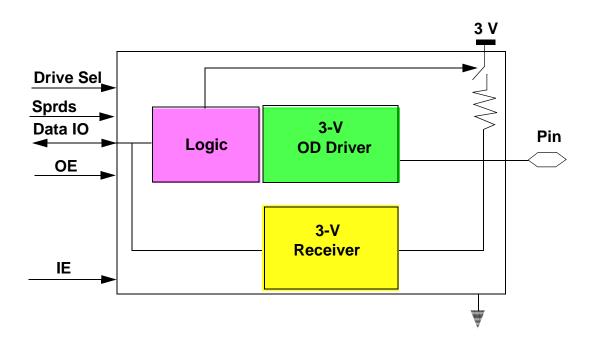

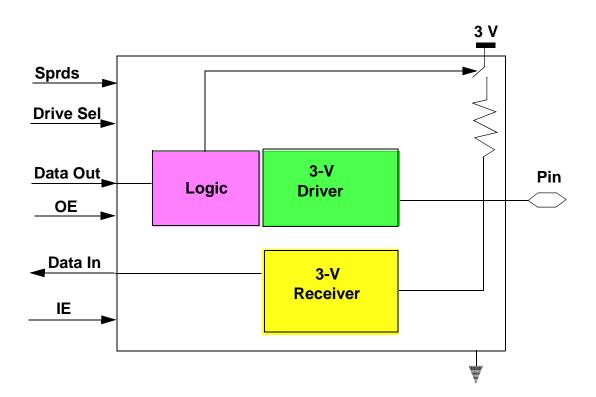

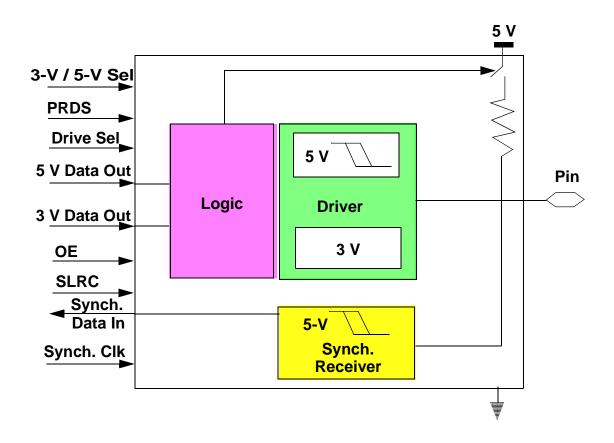

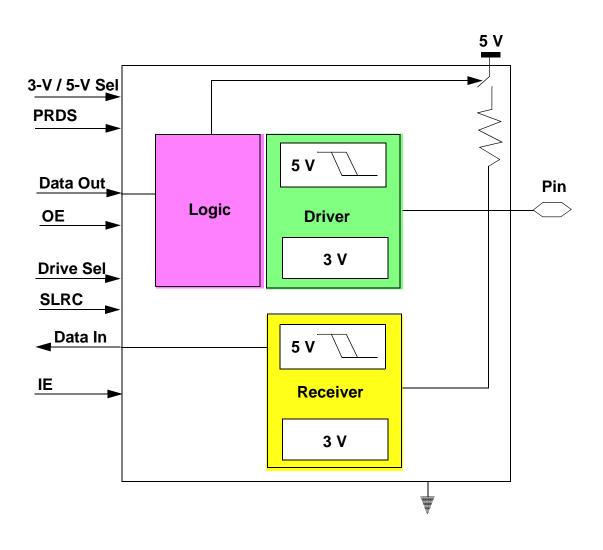

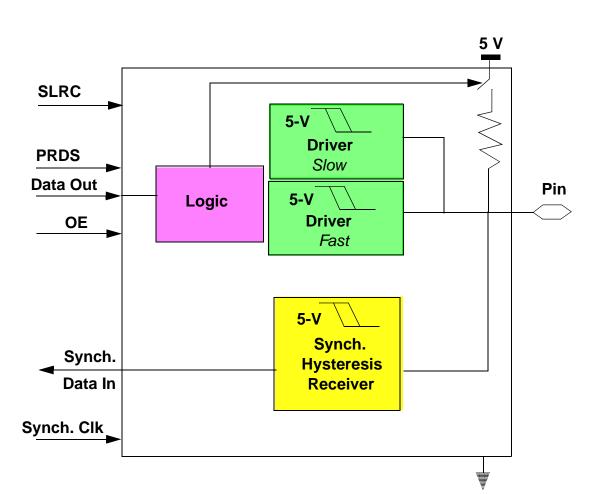

- Pad Type Functional pad structure used for a pin. For pad type descriptions, see 2.5 Pad Types.

|                                     |              | Ту     | /pe                  |                        |         | Slew Rate  | Drive            | Pad  |  |

|-------------------------------------|--------------|--------|----------------------|------------------------|---------|------------|------------------|------|--|

| Pin                                 | Function     | Driver | Receiver             | Direction <sup>1</sup> | Voltage | ns / 50 pF | Strength<br>(pF) | Type |  |

|                                     |              |        | USIU                 |                        |         |            |                  |      |  |

| ADDR[8:31]/                         | ADDR[8:31]   | TP     | _                    | I/O                    | 3 V     | _          | 25 / 50          |      |  |

| 00010410041                         | SGPIOA[8:31] | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | J    |  |

| DATA[0:31]/                         | DATA[0:31]   | TP —   |                      | I/O                    | 3 V     | _          | 25 / 50          |      |  |

| 0000000001                          | SGPIOD[0:31] | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | JD   |  |

| <u>IRQ[0]</u> /                     | IRQ[0]       |        | Hysteresis,<br>Synch | I                      | 3 V     | _          | _                | · IH |  |

| SGPIOC[0]                           | SGPIOC[0]    | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | ""   |  |

|                                     | IRQ[1]       | _      | Hysteresis,<br>Synch | I                      | 3 V     | _          | _                |      |  |

| IRQ[1]/RSV/<br>SGPIOC[1]            | RSV          | TP     | _                    | 0                      | 3 V     | _          | 25 / 50          | IH   |  |

|                                     | SGPIOC[1]    | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                |      |  |

|                                     | IRQ[2]       | _      | Hysteresis,<br>Synch | I                      | 3 V     | _          | _                |      |  |

| IRQ[2]/CR/                          | CR           | _      | _                    | I                      | 3 V     | _          | _                | IH   |  |

| SGPIOC[2]/MTS                       | SGPIOC[2]    | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                |      |  |

|                                     | MTS          | TP     | _                    | 0                      | 3 V     | 25 / 50    | _                |      |  |

| 100001110                           | ĪRQ[3]       | _      | Hysteresis,<br>Synch | I                      | 3 V     | _          | _                |      |  |

| IRQ[3]/KR,<br>RETRY/<br>SGPIOC[3]   | KR, RETRY    | TP     | _                    | I/O                    | 3 V     | _          | 25 / 50          | IH   |  |

|                                     | SGPIOC[3]    | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                |      |  |

|                                     | ĪRQ[4]       | _      | Hysteresis,<br>Synch | I                      | 3 V     | _          | _                |      |  |

| IRQ[4]/AT[2]/<br>SGPIOC[4]          | AT[2]        | TP     | _                    | 0                      | 3 V     | <u> </u>   | 25 / 50          | IH   |  |

|                                     | SGPIOC[4]    | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                |      |  |

| ĪRQ[5]/                             | IRQ[5]       | _      | Hysteresis,<br>Synch | I                      | 3 V     | _          | _                |      |  |

| SGPIOC[5]/<br>MODCK[1] <sup>2</sup> | SGPIOC[5]    | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | IH   |  |

|                                     | MODCK[1]     |        |                      | I                      | 3 V     |            |                  |      |  |

|                         |                 | Ту     | <b>/pe</b>                  | <b>.</b> 1             |         | Slew Rate  | Drive            | Pad      |

|-------------------------|-----------------|--------|-----------------------------|------------------------|---------|------------|------------------|----------|

| Pin                     | Function        | Driver | Receiver                    | Direction <sup>1</sup> | Voltage | ns / 50 pF | Strength<br>(pF) | Туре     |

| IRQ[6:7]/               | ĪRQ[6:7]        | _      | Hysteresis,<br>Synch        | I                      | 3 V     | _          | _                | СН       |

| MODCK[2:3] <sup>2</sup> | MODCK[2:3]      | _      | _                           | I                      | 3 V     | _          | _                |          |

| TSIZ[0:1]               | TSIZ[0:1]       | TP     | _                           | I/O                    | 3 V     | _          | 25 / 50          | F        |

| RD/WR                   | RD/WR           | TP     | _                           | I/O                    | 3 V     | _          | 25 / 50          | F        |

| BURST                   | BURST           | TP     | _                           | I/O                    | 3 V     | _          | 25 / 50          | F        |

| BDIP                    | BDIP            | TP     | _                           | I/O                    | 3 V     | _          | 25 / 50          | F        |

| TS <sup>3</sup>         | TS              | ANG    | _                           | I/O                    | 3 V     | _          | 25 / 50          | Е        |

| TA <sup>3</sup>         | TA              | ANG    | _                           | I/O                    | 3 V     | _          | 25 / 50          | Е        |

| TEA                     | TEA             | OD     | _                           | I/O                    | 3 V     | _          | 25 / 50          | Е        |

| RSTCONF/                | RSTCONF         | _      | _                           | I                      | 3 V     | _          | _                | . E      |

| TEXP <sup>2</sup>       | TEXP            |        | _                           | 0                      | 3 V     | _          | 25 / 50          |          |

| ŌĒ                      | <u>OE</u>       | TP     | _                           | 0                      | 3 V     | _          | <b>—</b> 25 / 50 |          |

| DI/OTO                  | BI <sup>3</sup> | ANG    | _                           | I/O                    | 3 V     | _          | 25 / 50          | _        |

| BI/515                  | BI/STS<br>STS   |        | _                           | 0                      | 3 V     | _          | 25 / 50          | E        |

| CS[0:3]                 | CS[0:3]         | TP     | _                           | 0                      | 3 V     | _          | 25 / 50          | Α        |

| WE[0:3]/BE[0:3]/        | WE[0:3]/BE[0:3] | TP     | _                           | 0                      | 3 V     | _          | 25 / 50          | F        |

| AT[0:3]                 | AT[0:3]         | TP     | _                           | 0                      | 3 V     | _          | 25 / 50          | <b>Т</b> |

| PORESET <sup>2</sup>    | PORESET         | _      | Hysteresis<br>Glitch filter | I                      | 3 V     | _          | _                | CNH      |

| HRESET <sup>2</sup>     | HRESET          | OD     | Hysteresis<br>Glitch filter | I/O                    | 3 V     | _          | 25 / 50          | ЕОН      |

| SRESET,2                | SRESET          | OD     | Hysteresis<br>Glitch filter | I/O                    | 3 V     | _          | 25 / 50          | EOH      |

| SGPIOC[6]/FRZ/          | SGPIOC[6]       |        | Hysteresis,<br>Synch        | I/O                    | 5 V     | 200 / fast | _                |          |

| PTR FRZ                 |                 | TP     | _                           | 0                      | 3 V     | _          | 25 / 50          | ı        |

|                         | PTR             |        | _                           | 0                      | 3 V     | _          | 25 / 50          |          |

| SGPIOC[7]/              | SGPIOC[7]       | TP     | Hysteresis,<br>Synch        | I/O                    | 5 V     | 200 / fast | _                |          |

| IRQOUT/LWP[0]           | IRQOUT          | TP     | _                           | 0                      | 3 V     | _          | 25 / 50          | ı        |

|                         | LWP[0]          | TP     | _                           | 0                      | 3 V     | _          | 25 / 50          |          |

2-8

|                      |                 | Ту     | <b>/pe</b>         |                        |         | Slew Rate  | Drive            | Pad  |

|----------------------|-----------------|--------|--------------------|------------------------|---------|------------|------------------|------|

| Pin                  | Function        | Driver | Receiver           | Direction <sup>1</sup> | Voltage | ns / 50 pF | Strength<br>(pF) | Type |

| BG/                  | BG              | TP     | _                  | I/O                    | 3 V     | _          | 25 / 50          |      |

| VF[0]/               | VF[0]           | TP     | _                  | 0                      | 3 V     | _          | 25 / 50          | G    |

| LWP[1]               | LWP[1]          | TP     | _                  | 0                      | 3 V     | _          | 25 / 50          | -    |

| BR/                  | BR              | TP     | _                  | I/O                    | 3 V     | _          | 25 / 50          |      |

| VF[1]/               | VF[1]           | TP     | _                  | 0                      | 3 V     | _          | 25 / 50          | G    |

| IWP[2]               | IWP[2]          | TP     | _                  | 0                      | 3 V     | _          | 25 / 50          |      |

| BB/                  | BB <sup>3</sup> | ANG    | _                  | I/O                    | 3 V     | _          | 25 / 50          |      |

| VF[2]/               | VF[2]           | TP     | _                  | 0                      | 3 V     | _          | 25 / 50          | G    |

| IWP[3]               | WP[3]           |        | _                  | 0                      | 3 V     | _          | 25 / 50          | -    |

| IWP[0:1]/            | IWP[0:1]        | TP     | _                  | 0                      | 3 V     | _          | 25 / 50          |      |

| VFLS[0:1]            | VFLS[0:1]       | TP     | _                  | 0                      | 3 V     | _          | 25 / 50          | A    |

| TMS                  | TMS             | _      | _                  | I                      | 3 V     | _          | _                | С    |

| TD1/D0D1             | TDI             | _      | _                  | I                      | 3 V     | _          | _                |      |

| TDI/DSDI             | DSDI            | _      | _                  | I                      | 3 V     | _          | _                | С    |

| TOLLIDOOLL           | тск             | _      | _                  | I                      | 3 V     | _          | _                |      |

| TCK/DSCK             | DSCK            | _      | _                  | I                      | 3 V     | _          | _                | D    |

| TD 0 /D 0 D 0        | TDO             | TP     | _                  | 0                      | 3 V     | _          | 25 / 50          |      |

| TDO/DSDO             | DSDO            | TP     | _                  | 0                      | 3 V     | _          | 25 / 50          | A    |

| TRST                 | TRST            | _      | _                  | I                      | 3 V     | _          | _                | С    |

| XTAL <sup>2</sup>    | XTAL            | TP     | _                  | 0                      | 3 V     | _          | _                | _    |

| EXTAL <sup>2</sup>   | EXTAL           | _      | _                  | I                      | 3 V     | _          | _                | _    |

| XFC                  | XFC             | _      | _                  | I/O                    | 3 V     | _          | _                | _    |

| CLKOUT               | CLKOUT          | TP     | _                  | 0                      | 3 V     | _          | 45 / 90          | В    |

| EXTCLK <sup>2</sup>  | EXTCLK          | _      | _                  | I                      | 3 V     | _          | _                | _    |

| ENGOLIZIDLIOLIZ      | ENGCLK          | TP     | _                  | 0                      | 5 V     | _          | 45 / 90          |      |

| ENGCLK/BUCLK         | BUCLK           | TP     | _                  | 0                      | 5 V     | _          | 45 / 90          | S    |

|                      |                 |        | QSMCM              |                        |         |            |                  | •    |

|                      | PCS0            | TP/OD  | Synch/<br>No Synch | I/O                    | 5 V     | 50 / fast  | _                |      |

| PCS0/<br>SS/QGPIO[0] | SS              | TP/OD  | Synch/<br>No Synch | I/O                    | 5 V     | 50 / fast  | _                | 0    |

|                      | QGPIO[0]        | TP/OD  | Synch/<br>No Synch | I/O                    | 5 V     | 50 / fast  | _                |      |

# **Table 2-2 Pin Functionality Table (Continued)**

| _,                         |                       | Ту     | /pe                  | <b>.</b> 1             |         | Slew Rate  | Drive            | Pad  |

|----------------------------|-----------------------|--------|----------------------|------------------------|---------|------------|------------------|------|

| Pin                        | Function              | Driver | Receiver             | Direction <sup>1</sup> | Voltage | ns / 50 pF | Strength<br>(pF) | Туре |

| PCS[1:3]/                  | PCS[1:3]              | TP/OD  | Synch                | I/O                    | 5 V     | 50 / fast  | _                | _    |

| QGPIO[1:3]                 | QGPIO[1:3]            | TP/OD  | Synch                | I/O                    | 5 V     | 50 / fast  | _                | 0    |

| MISO/QGPIO[4]              | MISO                  | TP/OD  | Synch/<br>No Synch   | I/O                    | 5 V     | 50 / fast  | _                | 0    |

| MISO/QGPIO[4]              | QGPIO[4]              | TP/OD  | Synch/<br>No Synch   | I/O                    | 5 V     | 50 / fast  | _                | U    |

| MOSI/QGPIO[5]              | MOSI                  | TP/OD  | Synch/<br>No Synch   | I/O                    | 5 V     | 50 / fast  |                  | 0    |

| MO3//QGFIO[3]              | QGPIO[5]              | TP/OD  | Synch/<br>No Synch   | I/O                    | 5 V     | 50 / fast  |                  | O    |

| SCK/QGPIO[6]               | SCK                   | TP/OD  | Synch/<br>No Synch   | I/O                    | 5 V     | 50 / fast  | _                | 0    |

|                            | QGPIO[6]              | TP/OD  | Synch/<br>No Synch   | I/O                    | 5 V     | 50 / fast  |                  | O    |

| TXD[1:2]/                  | TXD[1:2]              | TP/OD  | _                    | 0                      | 5 V     | 200 / fast | _                | Q    |

| QGPO[1:2]                  | QGPO[1:2]             | TP/OD  | _                    | 0                      | 5 V     | 200 / fast | _                | Q    |

| RXD[1:2]/                  | RXD[1:2]              | _      | _                    | I                      | 5 V     | _          | _                | R    |

| QGPI[1:2]                  | QGPI[1:2]             | _      | _                    | ļ                      | 5 V     | _          | _                | K    |

| ECK                        | ECK                   | _      | _                    | 1                      | 5 V     | _          | _                | R    |

|                            |                       |        | MIOS                 |                        |         |            |                  |      |

| MDA[11:15]                 | MDA[11:15]            | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | Р    |

| MDA[27:31]                 | MDA[27:31]            | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | Р    |

| MPWM[0:3],<br>[16:19]      | MPWM[0:3],<br>[16:19] | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | Р    |

| V/E(0:2)/                  | VF[0:2]               | TP     | _                    | 0                      | 3 V     | _          | 25 / 50          |      |

| VF[0:2]/<br>MPIO32B[0:2]   | MPIO32B[0:2]          | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | Н    |

| \/FL 8[0.4]/               | VFLS[0:1]             | TP     | _                    | 0                      | 3 V     | _          | 25 / 50          |      |

| VFLS[0:1]/<br>MPIO32B[3:4] | MPIO32B[3:4]          | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | Н    |

| MPIO32B[5:15]              | MPIO32B[5:15]         | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | 0    |

|                            |                       |        | TPU_A/TPU            | _B                     |         |            |                  |      |

| A_TPUCH[0:15]              | TPUCH[0:15]           | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | Р    |

# **Table 2-2 Pin Functionality Table (Continued)**

| D'                     | <b>-</b>    | Ту     | /pe                  |                        | W. K.   | Slew Rate  | Drive            | Pad  |  |

|------------------------|-------------|--------|----------------------|------------------------|---------|------------|------------------|------|--|

| Pin                    | Function    | Driver | Receiver             | Direction <sup>1</sup> | Voltage | ns / 50 pF | Strength<br>(pF) | Туре |  |

| A_T2CLK                | T2CLK       | TP     | Hysteresis<br>Synch  | I/O                    | 5 V     | 200 / fast | _                | Р    |  |

| B_TPUCH[0:15]          | TPUCH[0:15] | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | Р    |  |

| B_T2CLK                | T2CLK       | TP     | Hysteresis,<br>Synch | I/O                    | 5 V     | 200 / fast | _                | Р    |  |

|                        |             |        | QADC_A/QAI           | DC_B                   |         |            |                  |      |  |

| ETRIG[1:2]             | ETRIG[1:2]  | _      | Synch                | I                      | 5 V     | _          | _                | N    |  |

|                        | AN0         | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN0/<br>ANW/           | ANW         | _      | Analog               | I                      | 5 V     | _          | _                | М    |  |

| PQB0                   | PQB0        | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                |      |  |

|                        | AN1         | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN1/ANX/PQB1           | ANX         | _      | Analog               | I                      | 5 V     | _          | _                | M    |  |

|                        | PQB1        | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                |      |  |

|                        | AN2         | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN2/ANY/PQB2           | ANY         | _      | Analog               | I                      | 5 V     | _          | _                | М    |  |

|                        | PQB2        | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                |      |  |

|                        | AN3         | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN3/ANZ/PQB3           | ANZ         | _      | Analog               | I                      | 5 V     | _          | _                | М    |  |

|                        | PQB3        | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                |      |  |

| AN[48:51]/             | AN[48:51]   | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| PQB[4:7]               | PQB[4:7]    | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                | М    |  |

|                        | AN[52:54]   | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN[52:54]/             | MA[0:2]     | OD     | _                    | 0                      | 5 V     | _          | _                | L    |  |

| MA[0:2]/PQA[0:2]       | PQA[0:2]    | OD     | Hysteresis,<br>Synch | I/O                    | 5 V     | _          | _                |      |  |

| ANIEE:E01/             | AN[55:56]   | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN[55:56]/<br>PQA[3:4] | PQA[3:4]    | OD     | Hysteresis,<br>Synch | I/O                    | 5 V     | _          | _                | L    |  |

# **Table 2-2 Pin Functionality Table (Continued)**

|                        |           | Т      | /pe                  | 1                      | W 14    | Slew Rate  | Drive            | Pad  |  |

|------------------------|-----------|--------|----------------------|------------------------|---------|------------|------------------|------|--|

| Pin                    | Function  | Driver | Receiver             | Direction <sup>1</sup> | Voltage | ns / 50 pF | Strength<br>(pF) | Туре |  |

| ANIEZ-E01/             | AN[57:59] | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN[57:59]/<br>PQA[5:7] | PQA[5:7]  | OD     | Hysteresis,<br>Synch | I/O                    | 5 V     | _          | _                | L    |  |

|                        | AN0       | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN0/ANW/PQB0           | ANW       | _      | Analog               | I                      | 5 V     | _          | _                | М    |  |

|                        | PQB0      | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                |      |  |

|                        | AN1       | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN1/ANX/PQB1           | ANX       | _      | Analog               | I                      | 5 V     | _          | _                | М    |  |

|                        | PQB1      | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                |      |  |

|                        | AN2       | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN2/ANY/PQB2           | ANY       | _      | Analog               | I                      | 5 V     | _          | _                | М    |  |

|                        | PQB2      | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                |      |  |

|                        | AN3       | _      | Analog               | I                      | 5 V     | _          | _                | М    |  |

| AN3/ANZ/PQB3           | ANZ       | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

|                        | PQB3      | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                |      |  |

| AN[48:51]/             | AN[48:51] | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| PQB[4:7]               | PQB[4:7]  | _      | Hysteresis,<br>Synch | I                      | 5 V     | _          | _                | М    |  |

|                        | AN[52:54] | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

|                        | MA[0:2]   | OD     | _                    | 0                      | 5 V     | _          | _                | L    |  |

| MA[0:2]/PQA[0:2]       | PQA[0:2]  | OD     | Hysteresis,<br>Synch | I/O                    | 5 V     | _          | _                |      |  |

| AN[55:56]/             | AN[55:56] | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| PQA[3:4]               | PQA[3:4]  | OD     | Hysteresis,<br>Synch | I/O                    | 5 V     | _          | _                | L    |  |

| AN(E7:E01/             | AN[57:59] | _      | Analog               | I                      | 5 V     | _          | _                |      |  |

| AN[57:59]/<br>PQA[5:7] | PQA[5:7]  | OD     | Hysteresis,<br>Synch | I/O                    | 5 V     | _          | _                | L    |  |

|                        |           | ТС     | UCAN_A/TOL           | JCAN_B                 |         |            |                  |      |  |

| A_CNTX0                | CNTX0_A   | TP/OD  | _                    | 0                      | 5 V     | 50 / fast  | _                | Q    |  |

| B_CNTX0                | CNTX0_B   | TP/OD  |                      | 0                      | 5 V     | 50 / fast  |                  | Q    |  |

| Di-                | Formation                  | Ту     | /pe                 | Di1                    | V-11    | Slew Rate  | Drive            | Pad  |

|--------------------|----------------------------|--------|---------------------|------------------------|---------|------------|------------------|------|

| Pin                | Function                   | Driver | Receiver            | Direction <sup>1</sup> | voitage | ns / 50 pF | Strength<br>(pF) | Туре |

| A_CNRX0            | A_CNRX0 CNRX0_A            |        | Synch / No<br>Synch | I                      | 5 V     | _          | _                | R    |

| B_CNRX0            | CNRX0_B                    | _      | Synch / No<br>Synch | I                      | 5 V     | _          | _                | R    |

|                    |                            |        | CMF                 |                        |         |            |                  |      |

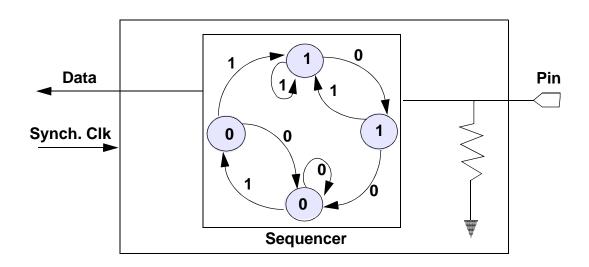

| EPEE               | EPEE                       | _      | Sequencer           | I                      | 3 V     | _          | _                | K    |

| VPP                | VPP                        | _      | _                   | I                      | 5 V     | _          | _                | _    |

|                    |                            | GI     | obal Power S        | upplies                |         |            |                  |      |

| VDDA               | VDDA                       | _      | _                   | I                      | 5 V     | _          | _                | _    |

| VDDF               | VDDF                       | _      | _                   | I                      | 3 V     | _          | _                | _    |

| VDDL               | VDDL                       | _      | _                   | I                      | 3 V     | _          | _                | _    |

| VDDH               | VDDH                       | _      | _                   | I                      | 5 V     | _          | _                | _    |

| VDDI               | VDDI                       | _      | _                   | I                      | 3 V     | _          | _                | _    |

| VDDSYN             | VDDSYN                     | _      | _                   | I                      | 3 V     | _          | _                | _    |

| VRH                | VRH                        | _      | _                   | I                      | 5 V     | _          | _                | _    |

| VRL                | VRL                        | _      | _                   | I                      |         | _          | _                | _    |

| VSSA               | VSSA                       | _      | _                   | I                      | _       | _          | _                | _    |

| VSSF               | VSSF                       | _      | _                   | I                      | _       | _          | _                | _    |

| VSSSYN             | VSSSYN VSSSYN              |        | _                   | I                      | _       | _          | _                | _    |

| KAPWR <sup>2</sup> | KAPWR <sup>2</sup> KAPWR — |        | _                   | I                      | 3 V     | _          | _                | _    |

| VDDSRAM            | VDDSRAM                    | _      | _                   | I                      | 3 V     | _          | _                | _    |

| VSS                | VSS                        | _      | _                   | I                      | _       | _          | _                | _    |

#### NOTES:

- 1. All inputs are 5-V friendly. All 5-V outputs are slow slew rate. The QSMCM and TouCAN pins have some slew rate control, but are faster than the general/purpose I/O and timer pins.

- 2. These pins are powered by KAPWR (Keep Alive Power Supply).

- 3. This pin is an active negate signal and may need an external pull-up resister.

## 2.3 Signal Descriptions

The pad ring supports 234 functional pins (284 including all power and ground). Each pin and the functionality it supports are described in this section. All references to timing in this document are numbers that are expected for a typical case process with a 50-pF load at 25°C. The supply voltages are assumed to be typical, as well: 5 V or 3.3 V. The 5-V supply is generally referred to as the 5-V supply, and the 3.3-V supply is referred to as the 3-V supply in this section.

#### 2.3.1 USIU Pads

## 2.3.1.1 ADDR[8:31]/SGPIOA[8:31]

Pin Name: addr\_sgpioa[8:31] (24 pins)

**Address Bus** – Specifies the physical address of the bus transaction. The address is driven onto the bus and kept valid until a transfer acknowledge is received from the slave. ADDR8 is the most significant signal for this bus.

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

## 2.3.1.2 DATA[0:31]/SGPIOD[0:31]

Pin Name: data\_sgpiod[0:31] (32 pins)

**Data Bus** – Provides the general purpose data path between the chip and all other devices. Although the data path is a maximum of 32 bits wide, it can be sized to support 8-, 16-, or 32-bit transfers. DATA[0] is the MSB of the data bus.

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

## 2.3.1.3 **IRQ[0]/SGPIOC[0]**

Pin Name: irq0\_b\_sgpioc0

**Interrupt Request** – One of the eight external lines that can request, by means of the internal interrupt controller, a service routine from the RCPU. IRQ0 is a nonmaskable interrupt (NMI).

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

## 2.3.1.4 IRQ[1]/RSV\_B/SGPIOC[1]

Pin Name: irq1\_b\_rsv\_b\_sgpioc1

**Interrupt Request** – One of the eight external lines that can request, by means of the internal interrupt controller, a service routine from the RCPU.

**Reservation** – This line used together with the address bus to indicate that the internal core initiated a transfer as a result of a STWCX or a LWARX instruction.

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

## 2.3.1.5 **IRQ[2]/CR\_B/SGPIOC[2]/MTS**

Pin Name: irq2\_b\_cr\_b\_sgpioc2\_mts

**Interrupt Request** – One of the eight external lines that can request, by means of the internal interrupt controller, a service routine from the RCPU.

**Cancel Reservation** – Instructs the chip to clear its reservation, some other master has touched its reserved space. An external bus snooper would assert this signal.

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

## 2.3.1.6 IRQ[3]/KR/RETRY/SGPIOC[3]

**Pin Name**: irq3\_b\_kr\_b\_retry\_b\_sgpioc3

**Interrupt Request** – One of the eight external lines that can request, by means of the internal interrupt controller, a service routine from the RCPU.

**Kill Reservation** – In case of a bus cycle initiated by a STWCX instruction issued by the CPU core to a non-local bus on which the storage reservation has been lost, this signal is used by the non-local bus interface to back-off the cycle.

**Retry** – Indicates to a master that the cycle is terminated but should be repeated. As an input, it is driven by the external slave to retry a cycle.

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

## 2.3.1.7 **IRQ[4]**/AT[2]/SGPIOC[4]

Pin Name: irq4\_b\_at2\_sgpioc4

**Interrupt Request** – One of the eight external lines that can request, by means of the internal interrupt controller, a service routine from the RCPU.

**Address Type** – A bit from the address type bus which indicates one of the 16 "address types" to which the address applies. The address type signals are valid at the rising edge of the clock in which the Special Transfer Start (STS) is asserted.

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

## 2.3.1.8 **IRQ[5]**/SGPIOC[5]/MODCK[1]

Pin Name: irq5\_b\_sgpioc5\_modck1

**Interrupt Request** – One of the eight external lines that can request, by means of the internal interrupt controller, a service routine from the RCPU.

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

**Mode Clock [1]** – Sampled at the negation of PORESET in order to configure the phase-locked loop (PLL)/clock mode of operation.

## 2.3.1.9 **IRQ[6:7]/MODCK[2:3]**

Pin Name: irq6\_b\_modck2 - irq7\_b\_modck3 (2 pins)

**Interrupt Request** – One of the eight external lines that can request, by means of the internal interrupt controller, a service routine from the RCPU.

**Mode Clock [2:3]** – Sampled at the negation of PORESET in order to configure the PLL/clock mode of operation.

## 2.3.1.10 TSIZ[0:1]

Pin Name: tsiz0 - tsiz1 (2 pins)

**Transfer size** – Indicates the size of the requested data transfer in the current bus cycle.

## 2.3.1.11 RD/WR

Pin Name: rd\_wr\_b

**Read/Write** – Indicates the direction of the data transfer for a transaction. A logic one indicates a read from a slave device; a logic zero indicates a write to a slave device.

#### 2.3.1.12 **BURST**

Pin Name: burst\_b

**Burst Indicator** – Indicates whether the current transaction is a burst transaction or not.

## 2.3.1.13 **BDIP**

Pin Name: bdip\_b

**Burst data in progress** – Indicates to the slave that there is a data beat following the current data beat.

### 2.3.1.14 TS

Pin Name: ts b

**Transfer Start** – Indicates the start of a bus cycle that transfers data to/from a slave device. This signal is driven by the master only when it gained the ownership of the bus. Every master should negate this signal before the bus relinquish. Every master should negate this signal before the bus is relinquished. This pin is an active negate signal and may need an external pull-up resistor to ensure proper operation and signal timing specifications.

#### 2.3.1.15 TA

Pin Name: ta b

**Transfer Acknowledge** – This line indicates that the slave device addressed in the current transaction has accepted the data transferred by the master (write) or has driven the data bus with valid data (read). The slave device negates the TA\_B signal after the end of the transaction and immediately three-state it to avoid contentions on the line if a new transfer is initiated addressing other slave devices. This pin is an

active negate signal and may need an external pull-up resistor to ensure proper operation and signal timing specifications.

## 2.3.1.16 TEA

Pin Name: tea\_b

**Transfer Error Acknowledge** – This signal indicates that a bus error occurred in the current transaction. The MCU asserts this signal when the bus monitor does not detect a bus cycle termination within a reasonable amount of time. The assertion of  $\overline{\text{TEA}}$  causes the termination of the current bus cycle, regardless of the state of  $\overline{\text{TEA}}$ . An external pull-up device is required to negate  $\overline{\text{TEA}}$  quickly, before a second error is detected. That is, the pin must be pulled up within one clock cycle of the time it was three-stated by the MPC555.

#### **2.3.1.17 RSTCONF/TEXP**

Pin Name: rstconf\_b\_texp

**Reset Configuration** – Input. This input line is sampled by the chip during the assertion of the HRESET signal in order to sample the reset configuration. If the line is asserted, the configuration mode will be sampled from the external data bus. When this line is negated, the configuration mode adopted by the chip will be the default one.

**Timer Expired** – This output line reflects the status of the TEXPS bit in the PLPRCR register in the USIU. This indicates an expired timer value.

#### 2.3.1.18 OE

Pin Name: oe b

**Output Enable** – This output line is asserted when a read access to an external slave controlled by the GPCM in the memory controller is initiated by the chip.

### 2.3.1.19 BI/STS

Pin Name: bi\_b\_sts\_b

**Burst Inhibit** – This bi-directional, active low, three-state line indicates that the slave device addressed in the current burst transaction is not able to support burst transfers. When the chip drives out the signal for a specific transaction, it asserts or negates  $\overline{\text{BI}}$  during the transaction according to the value specified by the user in the appropriate control registers. Negation of the signal occurs after the end of the transaction followed by the immediate three-state. This pin is an active negate signal and may need an external pull-up resistor to ensure proper operation and signal timing specifications.

**Special Transfer Start** – This output signal is driven by the chip to indicate the start of a transaction on the external bus or signals the beginning of an internal transaction in showcycle mode.

## 2.3.1.20 **CS**[0:3]

**Pin Name: cs0\_b - cs3\_b** (4 pins)

**Chip Select** – These output signals enable peripheral or memory devices at programmed addresses if defined appropriately in the memory controller.  $\overline{\text{CSO}}$  can be configured to be the global chip select for the boot device.

## 2.3.1.21 $\overline{WE[0:3]}/\overline{BE[0:3]}/AT[0:3]$

Pin Name: we\_b\_at[0:3](4 pins)

Write Enable[0:3]/Byte Enable[0:3] – This output line is asserted when a write access to an external slave controlled by the GPCM in the memory controller is initiated by the chip. It can be optionally be asserted on all read and write accesses. See WEBS bit definition in Table 10-7. WEO/BEO is asserted if the data lane DATA[0:7] contains valid data to be stored by the slave device. WE1/BE1 is asserted if the data lane DATA[8:15] contains valid data to be stored by the slave device. WE2/BE2 is asserted if the data line DATA[16:23] contains valid data to be stored by the slave device. WE3/BE3 is asserted if the data lane DATA[24:31] contains valid data to be stored by the slave device.

**Address Type** – Indicates one of the 16 address types to which the address applies. The address type signals are valid at the rising edge of the clock in which the Special Transfer Start (STS) is asserted.

#### 2.3.1.22 **PORESET**

Pin Name: poreset\_b

**Power on Reset** – This pin should be activated as a result of a voltage failure on the keep-alive power pins. The pin has a glitch detector to ensure that low spikes of less than 20 ns are rejected. The internal PORESET signal is asserted only if PORESET is asserted for more than 100 ns. See **SECTION 7 RESET** for more details on timing.

#### 2.3.1.23 **HRESET**

Pin Name: hreset\_b

Hard Reset – The chip can detect an external assertion of HRESET only if it occurs while the chip is not asserting reset. After negation of HRESET or SRESET is detected, a 16 cycles period is taken before testing the presence of an external reset. The internal HRESET signal is asserted only if HRESET is asserted for more than 100 ns. To meet external timing requirements, an external pull-up device is required to negate HRESET. See SECTION 7 RESET for more details on timing.

### 2.3.1.24 **SRESET**

**Pin Name**: sreset b

**Soft Reset** – The chip can detect an external assertion of SRESET only if it occurs while the chip is not asserting reset. After negation of HRESET or SRESET is

detected, a 16-cycle period is taken before testing the presence of an external soft reset. To meet external timing requirements, an external pull-up device is required to negate SRESET. See **SECTION 7 RESET** for more details on timing.

## 2.3.1.25 SGPIOC[6]/FRZ/PTR

Pin Name: sgpioc6\_frz\_ptr\_b

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

**Freeze** – Indicates that the RCPU is in debug mode.

**Program Trace** – Indicates an instruction fetch is taking place in order to allow program flow tracking.

## 2.3.1.26 SGPIOC[7]/IRQOUT/LWP[0]

Pin Name: sgpioc7\_irqout\_b\_lwp0

**SGPIO** – This function allows the pins to be used as general purpose inputs/outputs.

**Interrupt Out –** Indicates that an interrupt has been requested to all external devices.

**Load/Store Watchpoint 0** – This output line reports the detection of a data watchpoint in the program flow executed by the RCPU. See **SECTION 21 DEVELOPMENT SUPPORT** for more details.

## 2.3.1.27 **BG/VF[0]/LWP[1]**

Pin Name: bg\_b\_vf0\_lwp1

**Bus Grant** – Indicates external data bus status. Is asserted low when the arbiter of the external bus grants to the specific master the ownership of the bus.

**Visible Instruction Queue Flush Status** – This output line together with VF1 and VF2 is output by the chip when a program instructions flow tracking is required by the user. VF report the number of instructions flushed from the instruction queue in the internal core. See **SECTION 21 DEVELOPMENT SUPPORT** for more details.

**Load/Store Watchpoint** – This output line reports the detection of a data watchpoint in the program flow executed by the RCPU.

## 2.3.1.28 BR/VF[1]/IWP[2]

Pin Name: br\_b\_vf1\_iwp2

**Bus Request** – Indicates that the data bus has been requested for external cycle.

**Visible Instruction Queue Flush Status** – This output line together with VF1 and VF2 is output by the chip when a program instructions flow tracking is required by the user. VF report the number of instructions flushed from the instruction queue in the internal core. See **SECTION 21 DEVELOPMENT SUPPORT** for more details.

**Instruction Watchpoint 2** – This output line reports the detection of an instruction watchpoint in the program flow executed by the RCPU.

## 2.3.1.29 BB/VF[2]/IWP[3]

Pin Name: bb\_b\_vf2\_iwp3

**Bus Busy** – Indicates that the master is using the bus. This pin is an active negate signal and may need an external pull-up resistor to ensure proper operation and signal timing specifications.

**Visible Instruction Queue Flush Status** – This output line together with VF0 and VF1 is output by the chip when a program instructions flow tracking is required by the user. VF report the number of instructions flushed from the instruction queue in the internal core.

**Instruction Watchpoint 3** – This output line reports the detection of an instruction watchpoint in the program flow executed by the internal core.

## 2.3.1.30 IWP[0:1]/VFLS[0:1]

Pin Name: iwp0\_vfls0 - iwp1\_vfls1 (2 pins)

**Instruction Watchpoint** – These output lines report the detection of an instruction watchpoint in the program flow executed by the RCPU.

**Visible History Buffer Flush Status** – These signals are output by the chip to enable program instruction flow tracking. They report the number of instructions flushed from the history buffer in the RCPU. See **SECTION 21 DEVELOPMENT SUPPORT** for details.

#### 2.3.1.31 TMS

Pin Name: tms

**Test Mode Select** – This input controls test mode operations for on-board test logic (JTAG).

#### 2.3.1.32 TDI/DSDI

Pin Name: tdi\_dsdi

**Test Data In** – This input is used for serial test instructions and test data for on-board test logic (JTAG).

**Development Serial Data Input** – This input line is the data in for the debug port interface. See **SECTION 21 DEVELOPMENT SUPPORT** for details.

#### 2.3.1.33 TCK/DSCK

Pin Name: tck dsck

**Test Clock** – This input provides a clock for on-board test logic (JTAG).

**Development Serial Clock** – This input line is the clock for the debug port interface. See **SECTION 21 DEVELOPMENT SUPPORT** for details.

#### 2.3.1.34 TDO/DSDO

Pin Name: tdo\_dsdo

**Test Data Out** – This output is used for serial test instructions and test data for onboard test logic (JTAG).

**Development Serial Data Output –** This output line is the data-out line of the debug port interface. See **SECTION 21 DEVELOPMENT SUPPORT** for details.

## 2.3.1.35 TRST

Pin Name: trst b

**Test Reset** – This input provides asynchronous reset to the test logic (JTAG).

For non-JTAG test applications, TRST should be connected to ground or PORESET via an external resistor.

#### 2.3.1.36 XTAL

Pin Name: xtal

**XTAL** – This output line is one of the connections to an external crystal for the internal oscillator circuitry.

#### 2.3.1.37 EXTAL

Pin Name: extal

**EXTAL** – This line is one of the connections to an external crystal for the internal oscillator circuitry. If this pin is unused, it must be grounded.

#### 2.3.1.38 XFC

Pin Name: xfc

**External Filter Capacitance** – This input line is the connection pin for an external capacitor filter for the PLL circuitry.

#### 2.3.1.39 CLKOUT

Pin Name: clkout

**Clock Out** – This output line is the clock system frequency. The CLKOUT drive strength can be configured to full strength, half strength, or disabled. The drive strength is configured using the COM[0:1] bits in the SCCR register in the USIU.

#### 2.3.1.40 EXTCLK

Pin Name: extclk

**EXTCLK** – Input. This is the external frequency source for the chip. If this is unused, the pin must be grounded.

#### 2.3.1.41 VDDSYN

Pin Name: vddsyn

**VDDSYN** – This is the power supply of the PLL circuitry.

#### 2.3.1.42 VSSSYN

Pin Name: vsssyn

**VSSSYN** – This is the power supply of the PLL circuitry.

#### 2.3.1.43 ENGCLK/BUCLK

Pin Name: engclk\_buclk

**ENGCLK** – This is the engineering clock output. Drive strength can be configured to full strength, half strength or disabled. The drive strength is configured using the EECLK[0:1] bits in the SCCR register in the SIU.

**BUCLK** – When the chip is in limp mode, it is operating from a less precise on-chip ring oscillator to allow the system to continue minimum functionality until the system clock is fixed. This backup clock can be seen externally based on the values of the EECLK[0:1] bits in the SCCR register in the USIU.

#### 2.3.2 QSMCM PADS

### 2.3.2.1 PCS0/SS/QGPIO[0]

Pin Name: pcs0\_ss\_b\_qgpio0

**PCS0** – This signal provides QSPI peripheral chip select 0.

**SS** – Assertion of this bi-directional signal places the QSPI in slave mode.

**QSPI GPIO[0]** – When this pin is not needed for a QSPI application it can be configured as a general purpose input/output.

#### 2.3.2.2 PCS(1:3)/QGPIO[1:3]

Pin Name: pcs1\_qgpio1 - pcs3\_qgpio3 (3 pins)

**PCS[1:3]** – These signals provide three QSPI peripheral chip selects.

**QGPIO[1:3]** – When these pins are not needed for QSPI applications they can be configured as a general purpose input/output.

## 2.3.2.3 MISO/QGPIO[4]

Pin Name: miso\_qgpio4

**Master-In Slave-Out (MISO)** – This bi-directional signal furnishes serial data input to the QSPI in master mode, and serial data output from the QSPI in slave mode.

**QGPIO[4]** – When this pin is not needed for a QSPI application it can be configured as a general purpose input/output.

### 2.3.2.4 MOSI/QGPIO[5]

Pin Name: mosi\_qgpio5

**Master-Out Slave-In (MOSI)** – This bi-directional signal furnishes serial data output from the QSPI in master mode and serial data input to the QSPI in slave mode.

**QGPIO[5]** – When this pin is not needed for a QSPI application it can be configured as a general purpose input/output.

## 2.3.2.5 SCK/QGPIO[6]

Pin Name: sck\_qgpio6

**SCK** – This bi-directional signal furnishes the clock from the QSPI in master mode or furnishes the clock to the QSPI in slave mode.

**QGPIO[6]** – When this pin is not needed for a QSPI application, it can be configured as a general purpose input/output. When the QSPI is enabled for serial transmitting, the pin can *not* function as a GPIO.

## 2.3.2.6 TXD[1:2]/QGPO[1:2]

Pin Name: txd1\_qgpo1 - txd2\_qgpo2 (2 pins)

**Transmit Data** – These output signals are the serial data outputs from the SCI1 and SCI2.

**QSCI GPO[1:2]** – When these pins are not needed for a SCI applications, they can be configured as general-purpose outputs. When the transmit enable bit in the SCI control register is set to a logic 1, these pins can *not* function as general purpose outputs

## 2.3.2.7 RXD[1:2]/QGPI[1:2]

Pin Name: rxd1\_qgpi1 - rxd2\_qgpi2 (2 pins)

**Receive Data –** These input signals furnish serial data inputs to the SCI1 and SCI2.

**QSCI GPI[1:2]** – When these pins are not needed for SCI applications they can be configured as general purpose inputs. When the receive enable bit in the SCI control register is set to a logic 1, these pins can *not* function as general purpose inputs.

#### 2.3.2.8 ECK

Pin Name: eck

**External Baud Clock (EBCK)** – This signal provides an external baud clock used by SCI1 and SCI2.

#### **2.3.3 MIOS PADS**

### 2.3.3.1 MDA[11], [13]

Pin Name: mda11, mda13 (2 pins)

**Double Action** – Each of these pins provide a path for two 16-bit input captures and two 16-bit output compares.

**Clock Input** – Each of these pins provide a clock input to the modulus counter submodule. MDA11 can be used as the clock input to the MMCSM6 modulus counter. MDA13 can be used as the clock input to the MMCSM22 modulus counter.

## 2.3.3.2 MDA[12], [14]

Pin Name: mda12, mda14, (2 pins)

**Double Action** – Each of these pins provide a path for two 16-bit input captures and two 16-bit output compares.

**Load Input** – Each of these pins provide a load input to the modulus counter submodule. MDA12 can be used as the load input to the MMCSM6 modulus counter. MDA14 can be used as the load input to the MMCSM22 modulus counter.

## 2.3.3.3 MDA[15], [27:31]

Pin Name: mda15, mda27 - mda31 (6 pins)

**Double Action** – Each of these pins provide a path for two 16-bit input captures and two 16-bit output compares.

## 2.3.3.4 MPWM[0:3], [16:19]

Pin Name: mpwm0 - mpwm3, mpwm16 - mpwm19 (8 pins)

**Pulse Width Modulation** – These pins provide variable pulse width output signals at a wide range of frequencies.

## 2.3.3.5 VF[0:2]/MPIO32B[0:2]

Pin Name: vf0\_mpio32b0 - vf2\_mpio32b2 (3 pins)

**Visible Instruction Queue Flush Status** – These lines output by the chip when Program instruction flow tracking is required by the user. VF reports the number of instructions flushed from the instruction queue in the internal core.

**MIOS GPIO** – This function allows the pins to be used as general-purpose inputs/outputs.

## 2.3.3.6 VFLS[0:1]/MPIO32B[3:4]

Pin Name: vfls0\_mpio32b3 - vfls1\_mpio32b4 (2 pins)

**Visible History Buffer Flush Status** – These signals are output by the chip to allow program instruction flow tracking. They report the number of instructions flushed from the history buffer in the RCPU. See **SECTION 21 DEVELOPMENT SUPPORT** for details.

**MIOS GPIO** – This function allows the pins to be used as general purpose inputs/outputs.

### 2.3.3.7 MPIO32B[5:15]

**Pin Name**: mpio32b5 - mpio32b15 (11 pins)

**MIOS GPIO** – This function allows the pins to be used as general purpose inputs/outputs.

### 2.3.4 TPU A/TPU B PADS

### 2.3.4.1 TPUCH[0:15]

**Pin Name**: a\_tpuch0 - a\_tpuch15 (16 pins for first TPU), b\_tpuch0 - b\_tpuch15 (16 pins for second TPU)

**TPU Channels** – These signals provide each TPU with 16 input/output programmable timed events.

### 2.3.4.2 T2CLK

Pin Name: a\_t2clk (1 pin for first TPU), b\_t2clk (1 pin for second TPU)

**T2CLK** – This signal is used to clock or gate the timer count register 2 (TCR2) within the TPU. This pin is an output-only in special test mode.

### 2.3.5 QADC A/QADC B PADS

#### 2.3.5.1 ETRIG[1:2]

Pin Name: etrig1 - etrig2

**ETRIG** – These are the external trigger inputs to the QADC\_A and QADC\_B modules. ETRIG[1] can be configured to be used by both QADC\_A and QADC\_B. Likewise, ETRIG[2] can be used for both QADC\_B and QADC\_A. The trigger input pins are associated with the scan queues.

### 2.3.5.2 AN[0]/ANW/PQB[0]

**Pin Name**: a\_an0\_anw\_pqb0 (1 pin for first QADC), b\_an0\_anw\_pqb0 (1 pin for second QADC)

**Analog Channel (AN0)** – Internally multiplexed input-only analog channels. Passed on as a separate signal to the QADC.

**Multiplexed Analog Input (ANW)** – Externally multiplexed analog input.

**Port (PQB0)** – Input-only port. This is a 5-V input. This path is synchronized in the pad. The input is level-shifted before it is sent internally to the QADC.

### 2.3.5.3 AN[1]/ANX/PQB[1]

**Pin Name**: a\_an1\_anx\_pqb1 (1 pin for first QADC), b\_an1\_anx\_pqb1 (1 pin for second QADC)

**Analog Channel (AN1)** – Internally multiplexed input-only analog channels. Passed on as a separate signal to the QADC.

Multiplexed Analog Input (ANX) - Externally multiplexed analog input.

**Port (PQB1)** – Input-only port. This is a 5-V input. This path is synchronized in the pad. The input is level-shifted before being sent internally to the QADC.

## 2.3.5.4 AN[2]/ANY/PQB[2]

**Pin Name**: a\_an2\_any\_pqb2 (1 pin for first QADC), b\_an2\_any\_pqb2 (1 pin for second QADC)

**Analog Channel (AN2)** – Internally multiplexed input-only analog channel. The input is passed on as a separate signal to the QADC.

**Multiplexed Analog Input (ANY)** – Externally multiplexed analog input.

**Port (PQB2)** – Input-only port. This is a 5-V input. This path is synchronized in the pad. The input is level-shifted before it is sent internally to the QADC.

## 2.3.5.5 AN[3]/ANZ/PQB[3]

**Pin Name**: a\_an3\_anz\_pqb3 (1 pin for first QADC), b\_an3\_anz\_pqb3 (1 pin for second QADC)

**Analog Input (AN3)** – Internally multiplexed input-only analog channel. The input is passed on as a separate signal to the QADC.

Multiplexed Analog Input (ANZ) – Externally multiplexed analog input.

**Port (PQB3)** – Input-only port. This is a 5-V input. This path is synchronized in the pad. The input is level-shifted before it is sent internally to the QADC.

## 2.3.5.6 AN[48:51]/PQB[4:7]

**Pin Name**: a\_an48\_pqb4 - a\_an51\_pqb7 (4 pins for first QADC), b\_an48\_pqb4 - b\_an51\_pqb7 (4 pins for second QADC).

**Analog Input (AN[48:51])** – Analog input channel. The input is passed on as a separate signal to the QADC.

**Port (PQB[4:7])** – Input-only port. Has a synchronizer with an input enable and clock. The input is level-shifted before it is sent internally to the QADC.

## 2.3.5.7 AN[52:54]/MA[0:2]/PQA[0:2]

**Pin Name**: a\_an52\_ma0\_pqa0 - a\_an54\_ma2\_pqa2 (3 pins for first QADC), b\_an52\_ma0\_pqa0 - b\_an54\_ma2\_pqa2 (3 pins for second QADC).

**Analog Input (AN[52:54])** – Input-only. The input is passed on as a separate signal to the QADC.

**Multiplexed Address (MA[0:2])** – Output. Provides a three-bit multiplexed address output to the external multiplexer chip to allow selection of one of the eight inputs.

Port (PQA[0:2]) - Bi-directional.

## 2.3.5.8 AN[55:59]/PQA[3:7]

**Pin Name**: a\_an55\_pqa3 - a\_an59\_pqa7 (5 pins for first QADC), b\_an55\_pqa3 - b\_an59\_pqa7 (5 pins for second QADC).

**Analog Input (AN[55:59])** – Input-only. The input is passed on as a separate signal to the QADC.

Port (PQA[3:7]) - Bi-directional.

### 2.3.5.9 VRH

Pin Name: vrh

**VRH** – Input pin for high reference voltage for the QADC A and QADC B modules.

#### 2.3.5.10 VRL

Pin Name: vrl

**VRL** – Input pin for low reference voltage for the QADC A and QADC B modules.

#### 2.3.5.11 VDDA

Pin Name: vdda

**VDDA** – Power supply input to analog subsystems of the QADC\_A and QADC\_B modules.

#### 2.3.5.12 VSSA

Pin Name: vssa

**VSSA** – Input. Ground level for analog subsystems of the QADC\_A and QADC\_B modules.

### 2.3.6 TOUCAN A/TOUCAN B PADS

#### 2.3.6.1 CNTX0

Pin Name: a\_cntx0 (1 pin for first CAN), b\_cntx0 (1 pin for second CAN)

**TouCAN Transmit Data 0 –** This signal is the serial data output.

### 2.3.6.2 CNRX0

Pin Name: a\_cnrx0 (1 pin for first CAN), b\_cnrx0 (1 pin for second CAN)

**TouCAN Receive Data –** This signal furnishes serial input data.

#### **2.3.7 CMF PADS**

#### 2.3.7.1 EPEE

Pin Name: epee

**EPEE** – Input. This control signal will externally control the program or erase operations.

#### 2.3.7.2 VPP

Pin Name: vpp

**VPP** – Input. Flash supply voltage (5-V supply) used during program and erase operations of the CMF.

#### 2.3.7.3 VDDF

Pin Name: vddf

**VDDF** – Flash core voltage input (3-V supply). This separate supply voltage is needed in order to reduce noise in the read path of CMF.

#### 2.3.7.4 VSSF

Pin Name: vssf

**VSSF** – Flash core zero supply input. This separate supply is needed in order to reduce noise in the read path of CMF.

### 2.3.8 GLOBAL POWER SUPPLIES

### 2.3.8.1 VDDL

Pin Name: vddl

**VDDL** – 3-V voltage supply input.

### 2.3.8.2 VDDH

Pin Name: vddh

**VDDH** – 5-V voltage supply input.

#### 2.3.8.3 VDDI

Pin Name: vddi

**VDDI** – 3-V voltage supply input for internal logic.

#### 2.3.8.4 VSSI

Pin Name: vssi

**VSSI** – Zero supply input for internal logic. In packaged devices, VSSI is not a separate input from VSS.

#### 2.3.8.5 KAPWR

Pin Name: kapwr

**Keep-Alive Power** – 3-V voltage supply input for the oscillator and keep-alive registers.

#### 2.3.8.6 VDDSRAM

Pin Name: vddsram

**SRAM Keep-Alive Power –** 3-V voltage supply input for the SRAM.

#### 2.3.8.7 VSS

Pin Name: vss

**VSS** – Ground level reference input.

#### 2.4 Reset State

All input pins, with the exception of the power supply and clock related pins, are "weakly pulled" to a value during reset by a 130-microampere resistor based on certain conditions. In reset state all I/O pins become inputs, and all outputs except clkout, hreset\_b, sreset\_b, will be pulled only by the pull-up/pull-down.

## 2.4.1 Pin Functionality out of Reset

The functionality out of reset of some pins that support multiple functionality is defined in the SIUMCR through the reset configuration word. For details on which multiplexed pins are configured by the reset configuration word and how they are configured, refer to **7.5.2 Hard Reset Configuration Word**.

The 3-V related pins have selectable output buffer drive strengths which are controlled by the COM[0] bit in the USIU's system clock and reset control register (SCCR). The control is as follows:

0x2F C03C

- 0 = 3-V bus pins full drive (50-pF load)\*

- 1 = 3-V bus pins reduced drive (25-pF load)

## 2.4.2 Pad Module Configuration Register (PDMCR)

PDMCR - Pad Module Configuration Register

The slew rate and weak pull-up/pull-down characteristics of some pins are controlled by bits in the PDMCR. This register resides in the SIU memory map. The contents of the PDMCR are illustrated below. The PORESET signal resets all the PDMCR bits asynchronously.

| I DIVI | OI (   | ı aa ı | riodaic | , 0011 | ngare | 20011 | Cogiote | <b>,</b> 1 |    |    |       |     | 0, | \ZI \ | ,030 |

|--------|--------|--------|---------|--------|-------|-------|---------|------------|----|----|-------|-----|----|-------|------|

| 0      | 1      | 2      | 3       | 4      | 5     | 6     | 7       | 8          | 9  | 10 | 11    | 12  | 13 | 14    | 15   |

| SLRC0  | SLRC1  | SLRC2  | SLRC3   | Rese   | erved | PRDS  | SPRDS   |            |    |    | Reser | ved |    |       |      |

| HARD I | RESET: |        |         |        |       |       |         |            |    |    |       |     |    |       |      |

| 0      | 0      | 0      | 0       | 0      | 0     | 0     | 0       | 0          | 0  | 0  | 0     | 0   | 0  | 0     | 0    |

|        |        |        |         |        |       |       |         |            |    |    |       |     |    |       |      |

| 16     | 17     | 18     | 19      | 20     | 21    | 22    | 23      | 24         | 25 | 26 | 27    | 28  | 29 | 30    | 31   |

|        |        |        |         |        |       |       | RESER   | VED        |    |    |       |     |    |       |      |

| HARD   | RESET: |        |         |        |       |       |         |            |    |    |       |     |    |       |      |

| 0      | 0      | 0      | 0       | 0      | 0     | 0     | 0       | 0          | 0  | 0  | 0     | 0   | 0  | 0     | 0    |

### **Table 2-3 PDMCR Bit Settings**

| Bit(s) | Name  | Description                                                                                                                                                                                                                                                                               |

|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

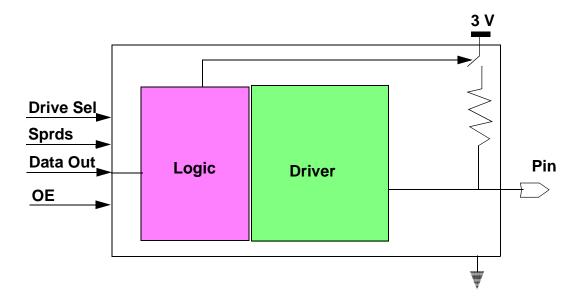

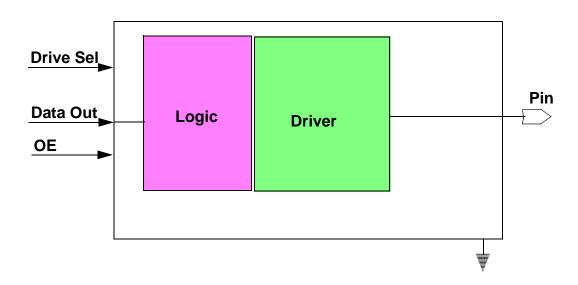

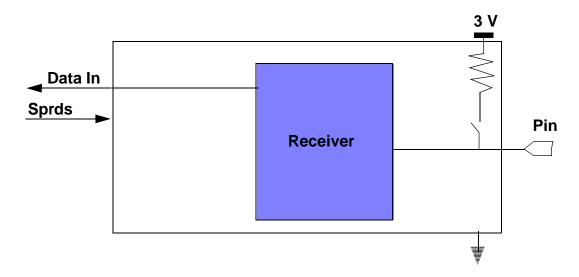

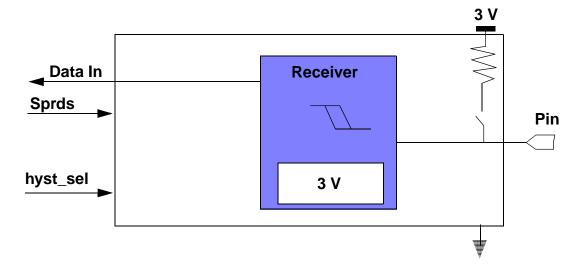

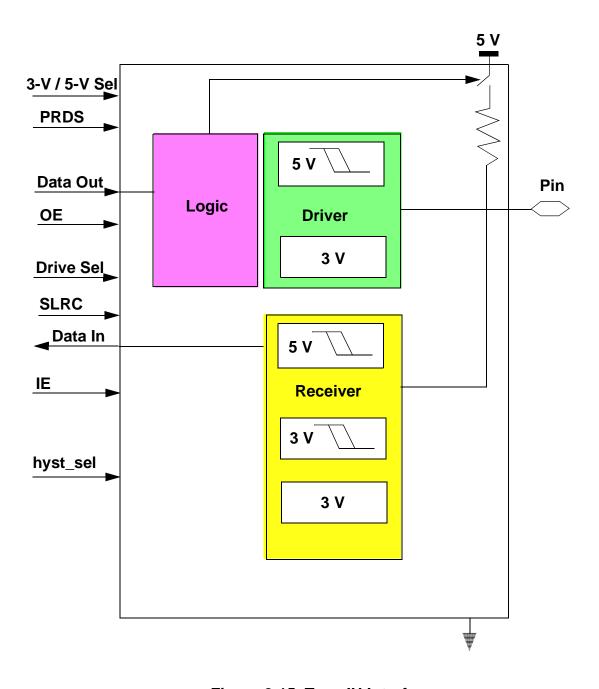

| 0      | SLRC0 | SLRC0 controls the slew rate of the following modules: TPU, QADC, USIU (SGPIO).  0 = Slow slew rate for pins. Controls slew rate pins of 200 ns.  1 = Normal slew rate for pins                                                                                                           |